# UNIVERSIDADE FEDERAL DO PARANÁ **DEPARTAMENTO DE ENGENHARIA ELÉTRICA SETOR DE TECNOLOGIA**

**CURITIBA**

2025

## TRABALHO DE CONCLUSÃO DE CURSO

Orientador: Prof. Marcelo de Souza

Coorientador: Prof.André Augusto Mariano

**CURITIBA**

2025

### **RESUMO**

O presente trabalho tem como objetivo apresentar o desenvolvimento de um amplificador de baixo ruído (LNA – Low Noise Amplifier) destinado a aplicações em rádios LoRa (Long Range), utilizando tecnologia CMOS de 130nm. O projeto foi conduzido até a etapa final de layout, com foco na viabilidade de implementação física e desempenho do circuito. Inicialmente, foi realizada uma revisão bibliográfica com o intuito de identificar os principais requisitos de projeto para LNAs. Além disso, foram analisadas diversas topologias de LNAs comumente empregadas em aplicações de comunicação sem fio. Com base nas informações coletadas na revisão bibliográfica, foi elaborado um projeto preliminar do circuito utilizando o ambiente de desenvolvimento Cadence Virtuoso, contemplando todas as etapas de desenvolvimento, na etapa de layout, o circuito foi implementado respeitando as regras de projeto (DRC) e foi realizada a extração de parasitas para simulação pós-layout. Os resultados obtidos demonstram que o LNA proposto atende aos requisitos mínimos estabelecidos, apresentando desempenho competitivo em relação a circuitos similares descritos na literatura.

Palavras chaves: LNA, LoRa, 895.5 MHz.

### **ABSTRACT**

This present work has as its objective to present the development of a low noise amplifier for LoRa radio applications, utilizing 130nm CMOS technology. The project was made until the final layout step, focusing on the physical implementation viability and the performance of the aforementioned amplifier. Initially a bibliographic review was done with the objective of identifying the main project requirements for LNAs, various commonly used LNA topologies for wireless communications were also analysed with the will of choosing the LNA topology that best fitted the project requirements. Utilizing the information obtained during the bibliographic review a circuit was developed using the Cadence Virtuoso design suite. Contemplating all the design steps up to the final layout. The circuit was implemented and a post layout parasite extraction was done for post layout simulation purposes. The final results obtained demonstrate that not only the proposed LNA does attend the minimum project requirements but it also does show a competitive performance compared to similar LNAs already described in the literature.

Keywords: LNA, LoRa, 895.5 MHz.

# SUMÁRIO

| 1 INTRODUÇÃO                                                        | 7  |

|---------------------------------------------------------------------|----|

| 1.1 Considerações Iniciais                                          | 7  |

| Equação 1: Fórmula de Friis para Ruído                              | 8  |

| 1.2 Objetivos e Metodologia                                         | 8  |

| 1.3 Banda de Interesse                                              | 10 |

| 1.4 PDK Utilizado                                                   | 11 |

| 2 FUNDAMENTOS TEÓRICOS                                              | 11 |

| 2.1 Topologias                                                      | 11 |

| 2.1.1 Amplificador de Porta Comum com Carga Indutiva                | 12 |

| Equação 2: Impedância de Entrada Amplificador Porta Comum           | 13 |

| 2.1.2 Amplificador Cascode de Porta Comum                           | 13 |

| Equação 3: Impedância de Entrada Amplificador Fonte Comum Cascode   | 14 |

| 2.1.3 Amplificador de Fonte Comum com Carga Indutiva                | 15 |

| Equação 4: Impedância de Entrada Amplificador Fonte Comum           | 15 |

| 2.1.4 Amplificador de Fonte Comum com Realimentação Resistiva       | 16 |

| Equação 6: Impedância de Entrada Amplificador Fonte Comum           | 17 |

| 2.1.5 Amplificador Cascode Fonte Comum com Degeneração Indutiva     | 18 |

| 2.1.6 Amplificadores Diferenciais                                   | 19 |

| 2.1.7 Topologia Escolhida                                           | 19 |

| 2.2 Casamento de Impedância de Entrada para um Cascode Degenerativo | 20 |

| Equação 7: Impedância de Entrada Amplificador Fonte Comum Cascode   | 21 |

| Equação 8: Impedância de Entrada Amplificador Fonte Comum Cascode   | 22 |

| 2.3 Indutor de Dreno e Casamento de Impedância de Saída             | 23 |

| 2.4 Figura de ruído                                                 | 23 |

| Equação 9: Figura de Ruído Amplificador Fonte Comum Cascode         | 23 |

| Equação 10: Impedância de Entrada Amplificador Fonte Comum Cascode  | 24 |

| Equação 11: Impedância de Entrada Amplificador Fonte Comum Cascode  | 24 |

| Equação 12: Impedância de Entrada Amplificador Fonte Comum Cascode  | 25 |

| 3 SIMULAÇÃO UTILIZANDO COMPONENTES IDEAIS                           | 25 |

| 3.1 Esquemático de Simulação                                        | 25 |

| 3.2 Resultados de Simulação                                         | 27 |

| 4 SIMULAÇÃO UTILIZANDO COMPONENTES REAIS                            | 31 |

| 4.1 Alterações do Circuito:                                         | 31 |

| 4.2 Esquemático de Simulação:                                       | 32 |

| 4.3 Resultados de Simulação:                                        | 33 |

| 4.4 Simulação de Corners:                                           |    |

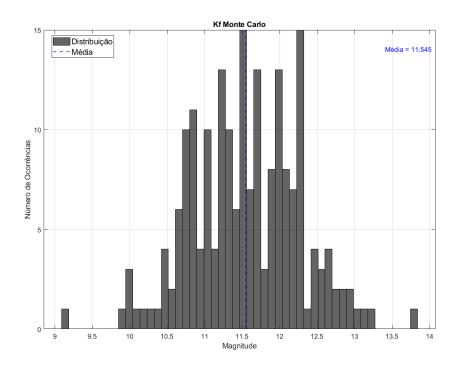

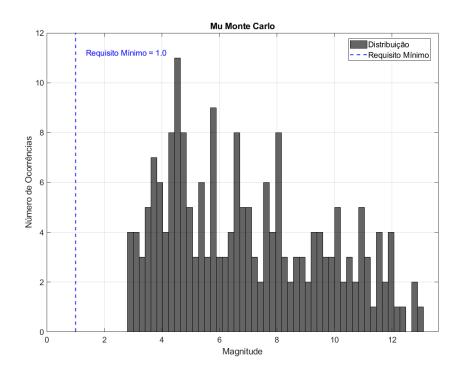

| 4.5 Simulação de Monte Carlo:                                       | 42 |

| 5 LAYOUT E SIMULAÇÃO COM EXTRAÇÃO DE PARASITAS                      | 46 |

| 5.1 Alterações do Circuito:                                         | 46 |

| 5.2 Layout da Parte Ativa:                                          | 47 |

| 5.3 Layout Completo:                                                | 48 |

| 5.4 Esquemático de Simulação:                                       | 51 |

| 5.5 Resultados de Simulação:                                        | 51 |

| 5.6 Simulação de Corners:                                           | 55 |

| 5.7 Simulação de Monte Carlo:                                       |    |

| 6 CONCLUSÃO                                                         | 62 |

| 0 CONCLUSAC                                                         |    |

## LISTA DE FIGURAS

| Figura 1: Diagrama de Blocos de um Rece   | ptor RF                                  | 8  |

|-------------------------------------------|------------------------------------------|----|

| Figura 2: Alocação de Frequências Rádio   | LoRa                                     | 11 |

| Figura 3: Esquemático Amplificador Porta  | Comum com Carga Indutiva                 | 13 |

|                                           | Comum Cascode com Carga Indutiva         |    |

| Figura 5: Esquemático Amplificador Fonte  | Comum com Carga Indutiva                 | 16 |

|                                           | Comum com Realimentação Resistiva        |    |

|                                           | ode Fonte Comum com Degeneração Indutiva |    |

|                                           | num com Degeneração Indutiva             |    |

| Figura 10: Entrada Amplificador Cascode   | Fonte Comum com Degeneração Indutiva     | 22 |

|                                           | ponentes Ideais                          |    |

| Figura 11: Parâmetro S11 Amplificador co  | m Componentes Ideais                     | 28 |

| Figura 13: Parâmetro S22 Amplificador co  | m Componentes Ideais                     | 29 |

| Figura 14: Parâmetro S21 Amplificador co  | m Componentes Ideais                     | 29 |

| Figura 15: Figura de Ruído Amplificador c | om Componentes Ideais                    | 30 |

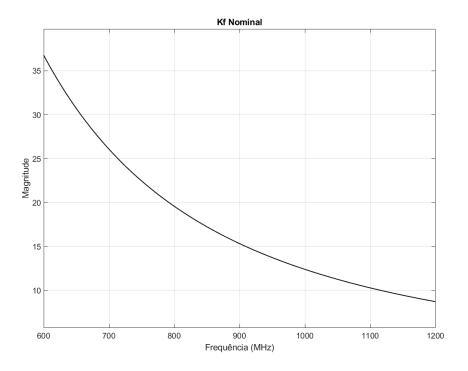

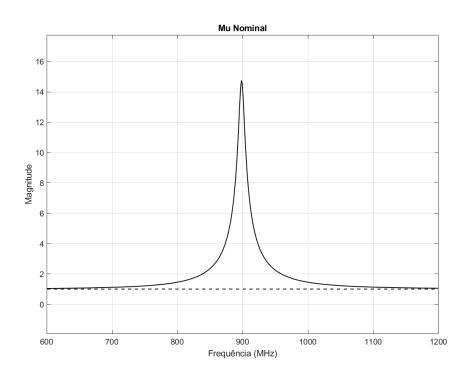

| Figura 16: Fator Kf Amplificador com Com  | ponentes Ideais                          | 30 |

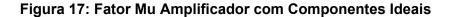

| Figura 17: Fator Mu Amplificador com Cor  | nponentes Ideais                         | 31 |

| Figura 18: Esquemático Amplificador com   | Componentes Reais                        | 33 |

| Figura 19: Esquemático de Simulação Am    | plificador com Componentes Reais         | 34 |

| Figura 20: Parâmetro S11 Amplificador co  | m Componentes Reais                      | 35 |

| Figura 22: Parâmetro S21 Amplificador co  | m Componentes Reais                      | 36 |

| Figura 23: Figura de Ruído Amplificador c | om Componentes Reais                     | 36 |

| Figura 24: Fator Kf Amplificador com Com  | ponentes Reais                           | 37 |

| Figura 25: Fator Mu Amplificador com Cor  | nponentes Reais                          | 37 |

| Figura 26: Parâmetro S11 Amplificador co  | m Componentes Reais Corners              | 39 |

| Figura 27: Parâmetro S22 Amplificador co  | m Componentes Reais Corners              | 40 |

| Figura 28: Parâmetro S21 Amplificador co  | m Componentes Reais Corners              | 40 |

| Figura 29: Figura de Ruído Amplificador c | om Componentes Reais Corners             | 41 |

|                                           | ponentes Reais Corners                   |    |

|                                           | nponentes Reais Corners                  |    |

| •                                         | m Componentes Reais Monte Carlo          |    |

| •                                         | m Componentes Reais Monte Carlo          |    |

| Figura 35: Figura de Ruído Amplificador c | om Componentes Reais Monte Carlo         | 45 |

| •                                         | mponentes Reais Monte Carlo              |    |

| •                                         | mponentes Reais Monte Carlo              |    |

|                                           | out                                      |    |

|                                           |                                          |    |

| Figura 40: Layout Amplificador Completo.  |                                          | 50 |

| Figura 41: Comparação Ilustrativa do Circ | uito                                     | 51 |

| Figura 42: Esquemático de Simulação Am    | plificador Layout                        | 52 |

| -                                         | yout                                     |    |

|                                           | yout                                     |    |

| •                                         | yout                                     |    |

|                                           | ayout                                    |    |

|                                           |                                          |    |

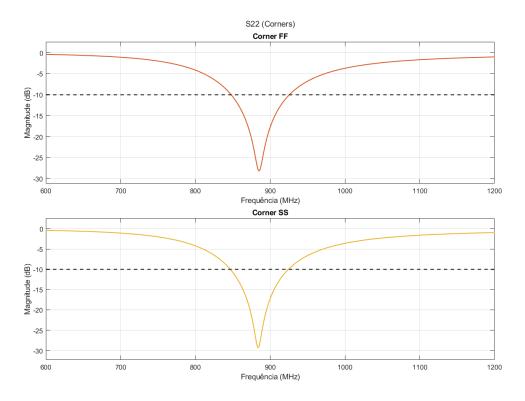

| Figura 49: Parâmetro S11 Amplificador La  | yout Corners                             | 57 |

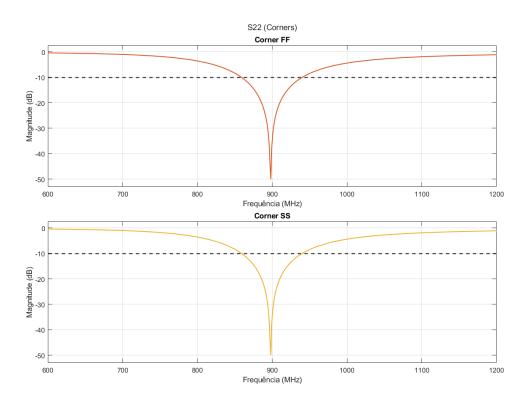

| Figura 50: Parâmetro S22 Amplificador Layout Corners                                 |    |  |  |

|--------------------------------------------------------------------------------------|----|--|--|

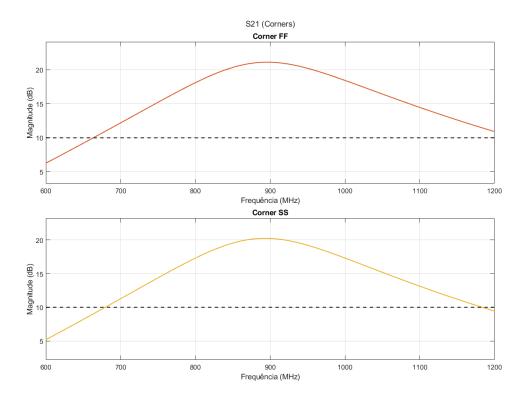

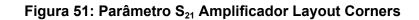

| Figura 51: Parâmetro S21 Amplificador Layout Corners                                 | 58 |  |  |

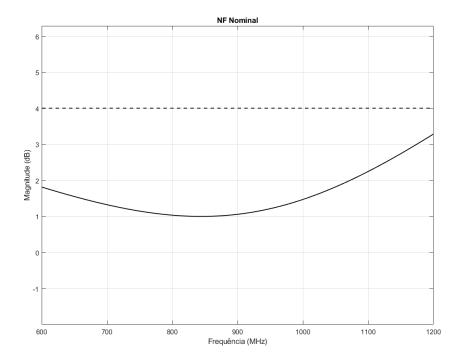

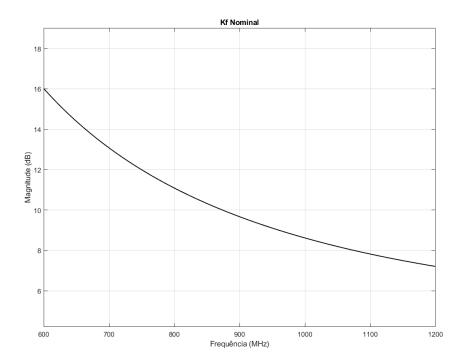

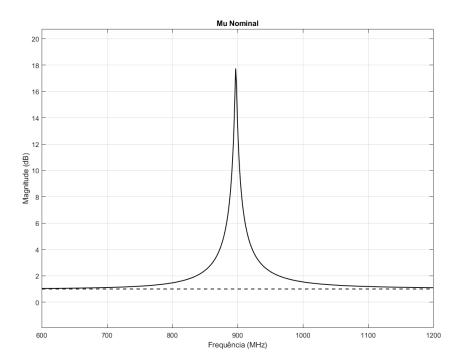

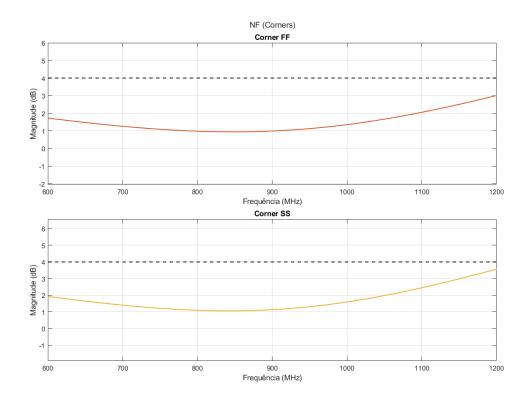

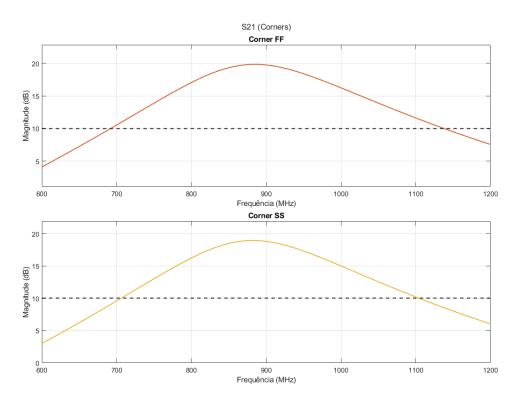

| Figura 52: Figura de Ruído Amplificador Layout Corners                               | 58 |  |  |

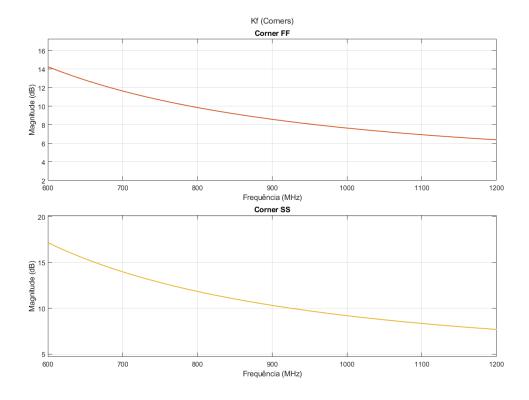

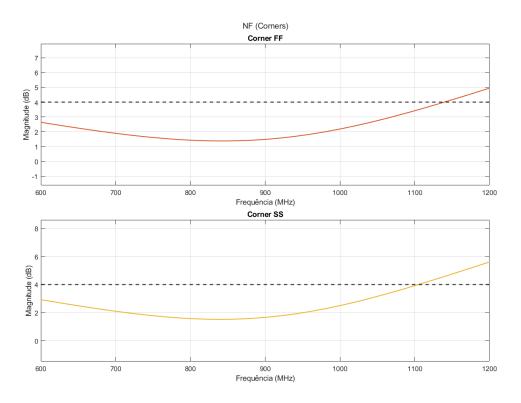

| Figura 53: Fator Kf Amplificador Layout Corners                                      | 59 |  |  |

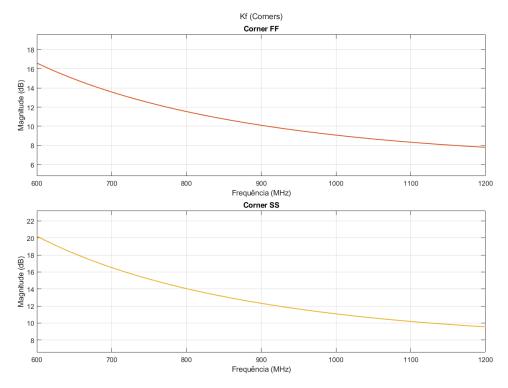

| Figura 54: Fator Mu Amplificador Layout Corners                                      | 59 |  |  |

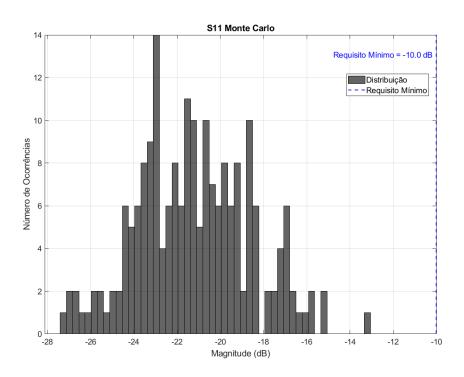

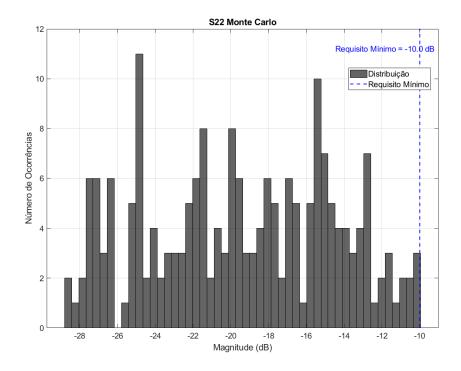

| Figura 55: Parâmetro S11 Amplificador Layout Monte Carlo                             | 61 |  |  |

| Figura 56: Parâmetro S22 Amplificador Layout Monte Carlo                             | 61 |  |  |

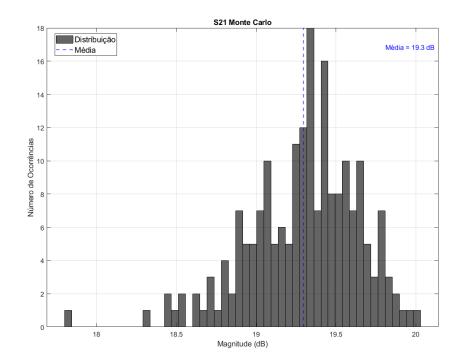

| Figura 57: Parâmetro S21 Amplificador Layout Monte Carlo                             | 62 |  |  |

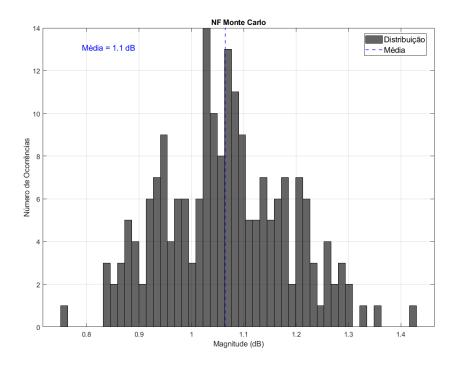

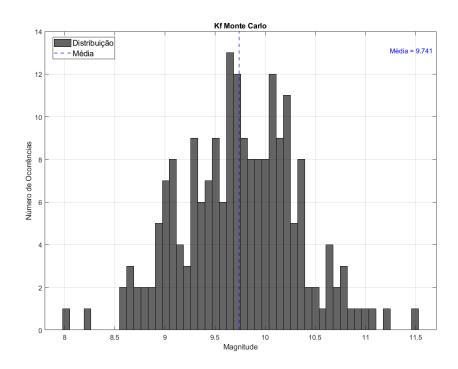

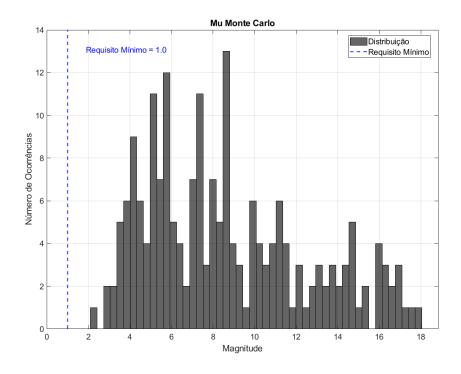

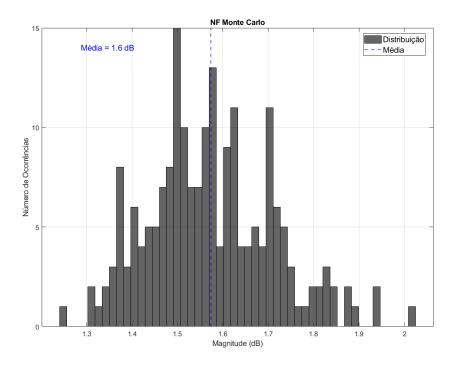

| Figura 58: Figura de Ruído Amplificador Layout Monte Carlo                           |    |  |  |

| Figura 59: Fator Kf Amplificador Layout Monte Carlo                                  |    |  |  |

| Figura 60: Fator Mu Amplificador Layout Monte Carlo                                  | 63 |  |  |

| Figura 61: RF Wafer Probe                                                            | 64 |  |  |

|                                                                                      |    |  |  |

|                                                                                      |    |  |  |

| LISTA DE TABELAS                                                                     |    |  |  |

| Tabela 1: Resultados de Simulação Amplificador com Componentes Ideais                | 27 |  |  |

| Tabela 2: Resultados de Simulação Amplificador com Componentes Reais                 | 34 |  |  |

| Tabela 3: Características dos Corners Utilizados                                     | 35 |  |  |

| Tabela 4: Resultados de Simulação de Corners Amplificador com Componentes Reais      | 38 |  |  |

| Tabela 5: Comparativo de Resultados de Simulação Esquemático/Layout                  | 52 |  |  |

| Tabela 6:Resultados de Simulação de Corners Layout                                   | 56 |  |  |

| Tabela 7: Comparativo entre o Amplificador Proposto e os Encontrados na Bibliografia | 61 |  |  |

| LISTA DE EQUAÇÕES                                                                    |    |  |  |

| Equação 1: Fórmula de Friis para Ruído                                               | 8  |  |  |

| Equação 2: Impedância de Entrada Amplificador Porta Comum                            | 13 |  |  |

| Equação 3: Impedância de Entrada Amplificador Fonte Comum Cascode                    | 14 |  |  |

| Equação 4: Impedância de Entrada Amplificador Fonte Comum                            | 15 |  |  |

| Equação 6: Impedância de Entrada Amplificador Fonte Comum                            | 17 |  |  |

| Equação 7: Impedância de Entrada Amplificador Fonte Comum Cascode                    | 21 |  |  |

| Equação 8: Impedância de Entrada Amplificador Fonte Comum Cascode                    | 22 |  |  |

| Equação 9: Figura de Ruído Amplificador Fonte Comum Cascode                          | 23 |  |  |

| Equação 10: Impedância de Entrada Amplificador Fonte Comum Cascode                   | 24 |  |  |

| Equação 11: Impedância de Entrada Amplificador Fonte Comum Cascode                   | 24 |  |  |

| Equação 12: Impedância de Entrada Amplificador Fonte Comum Cascode                   | 25 |  |  |

|                                                                                      |    |  |  |

## 1 INTRODUÇÃO

### 1.1 Considerações Iniciais

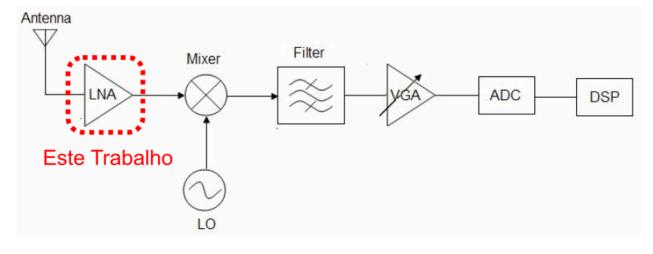

Com a popularização das comunicações sem fio, a demanda por equipamentos responsáveis pelo tratamento e demodulação de sinais de radiofrequência recebidos aumentou significativamente. Para garantir que essas operações sejam realizadas de forma eficaz, é essencial o uso de amplificadores de baixo ruído (*Low Noise Amplifier* - LNA) na entrada de receptores de radiofrequência. Esses dispositivos amplificam sinais de baixa potência e SNR (*Signal To Noise Ratio* - relação sinal ruído), recebidos pela antena, minimizando as perdas em linhas de transmissão e fazendo com que o sinal recebido possa ser utilizado de forma adequada pelos estágios subsequentes de um receptor de radiofrequências, na Figura 1 está um diagrama de blocos para um receptor de radiofrequência com o LNA destacado:

Figura 1: Diagrama de Blocos de um Receptor RF

Fonte: Creative Commons Attribution-NonCommercial 4.0 International

Segundo a equação de Friis a figura de ruído total de um sistema com n estágios é dada pela seguinte expressão:

Equação 1: Fórmula de Friis para Ruído

$$F_{total} = F_1 + \frac{F_2}{G_1} + \frac{F_3}{G_1 G_2} + \dots \frac{F_n}{G_1 G_2 \dots G_{n-1}}$$

Fonte: J.D. Kraus, Radio Astronomy, McGraw-Hill, 1966.

Nesta equação os termos F representam as figuras de ruído de cada estágio de 1 até n enquanto os termos G representam os ganhos de cada estágio. De acordo com esta expressão a figura de ruído total do sistema é dada pela figura de ruído do primeiro estágio adicionada da figura de ruído dos estágios subsequentes divididas pelo produto do ganho dos estágios anteriores, dessa forma podemos inferir que a figura de ruído de um sistema com n estágios é dominada pela figura de ruído do primeiro estágio, enquanto o ruído dos estágios subsequentes é dividido pelo ganho do primeiro estágio, por este motivo o primeiro estágio do sistema deve ter uma figura de ruído pequena e um ganho alto de forma a minimizar a figura de ruído total do sistema.

### 1.2 Objetivos e Metodologia

Este trabalho terá como objetivos realizar a revisão bibliográfica de forma a analisar as topologias disponíveis para LNAs descritas na literatura e projetar um LNA de banda curta para radio LoRa(Long Range) em circuito integrado até o estágio de layout para produção, de forma que o discente responsável ao final do trabalho obtenha conhecimentos em processos de desenvolvimento e layout de microeletrônica de RF, o projeto foi realizado utilizando o PDK (Physical Design Kit) CMRF8SF de 130nm da fabricante Global Foundries. Este circuito infelizmente não será fabricado devido aos altos custos atrelados a produção de protótipos desta tecnologia tornando a produção de um protótipo físico de teste inviável para este trabalho.

As metodologias utilizadas para este trabalho são a revisão bibliográfica para analisar e elencar a topologia mais viável descrita na bibliografia dentro do escopo deste projeto e a utilização de software de simulação e layout para implementar e aferir a viabilidade de fabricação do projeto.

Listando os objetivos em ordem cronológica temos a seguinte lista:

- 1. Realizar uma revisão bibliográfica, analisando e elencando a topologia mais adequada para a realização do projeto final;

- Implementar no software Cadence Virtuoso um circuito de simulação para a topologia escolhida na etapa anterior, utilizando componentes passivos ideais e transistores de radiofrequência 130 nm da biblioteca CMRF8SF;

- Implementar no software Cadence Virtuoso um circuito de simulação baseado no circuito final da etapa anterior utilizando componentes reais para determinar o comportamento do circuito de forma mais realista;

- 4. Desenvolver um layout do circuito da etapa anterior para produção de circuito integrado utilizando a ferramenta de layout do software Cadence Virtuoso.

Para o projeto foram escolhidos requisitos de performance mínimos para o layout final com base nos requisitos utilizados no livro Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012. Os requisitos utilizados estão a seguir:

- Entrada e saída do amplificador casadas em 50Ω na frequência central;

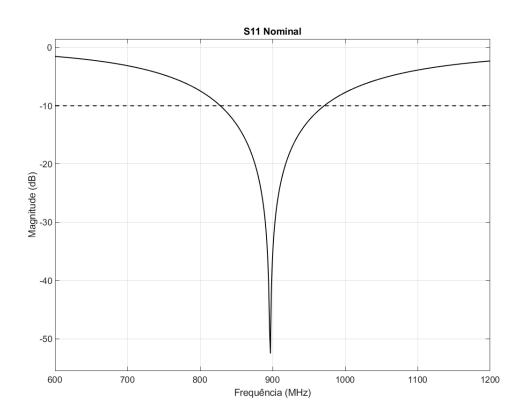

- O circuito deve ter uma perda por reflexão de no máximo 10% na entrada, na frequência central, portanto o coeficiente de reflexão S<sub>11</sub> da entrada deve ser de no mínimo -10 dB na frequência central;

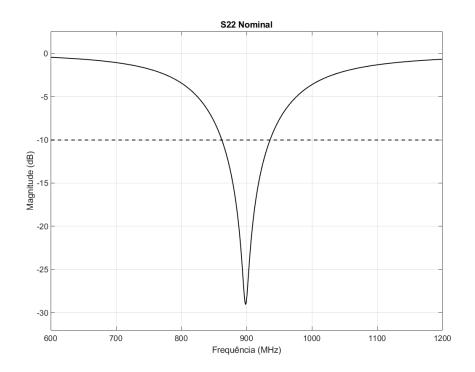

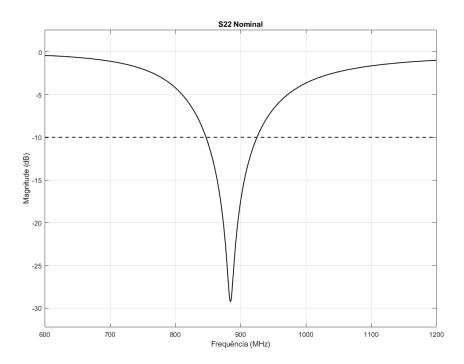

- O circuito deve ter uma perda por reflexão de no máximo 10% na saída, na frequência central portanto o coeficiente de reflexão S<sub>22</sub> da saída deve ser de no mínimo -10 dB na frequência central;

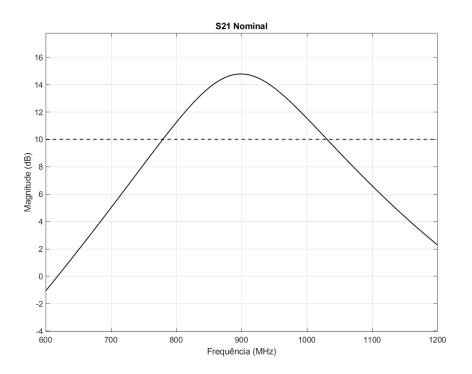

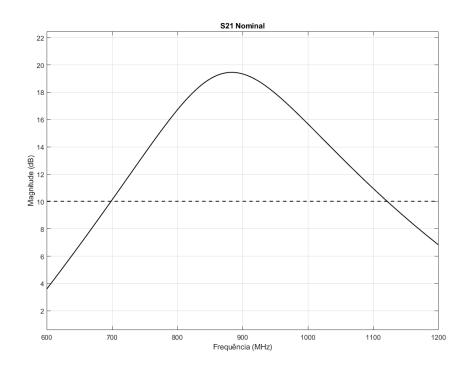

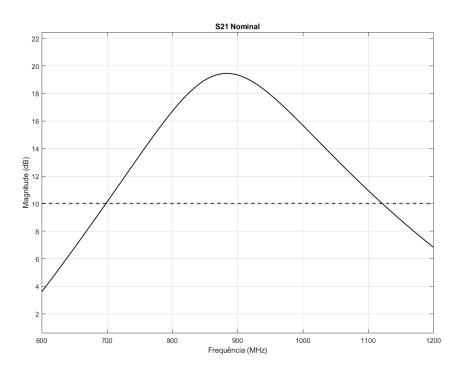

- O circuito deve possuir o ganho mínimo esperado de um LNA, portanto o coeficiente de transmissão direta S<sub>21</sub> deve ser de no mínimo 10 dB na frequência central;

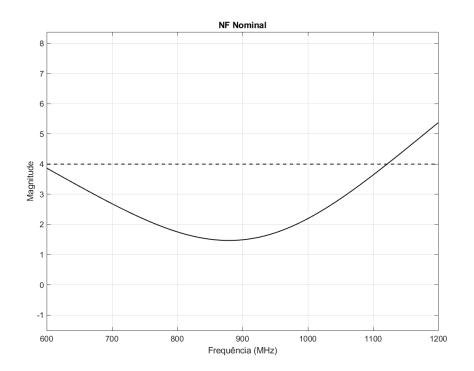

- O circuito deve possuir uma figura de ruído inferior a máxima esperada para um LNA, portanto a figura de ruído deve ser inferior a 4 dB na frequência central.

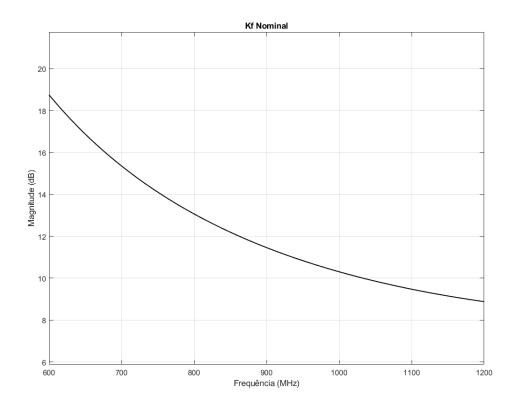

- O circuito deve ser estável na faixa de operação, portanto os fatores de estabilidade Mu e Kf superiores a 1 na banda de interesse;

- Alimentação em 1,5V visto que é a tensão nominal indicada no manual do PDK

### 1.3 Banda de Interesse

Para este trabalho foi determinado que a banda a ser amplificada seria a banda alocada para rádio LoRa, esta tecnologia é utilizada para transmissão de dados com uma taxa de transmissão baixa porém em longa distâncias já que a frequência utilizada para transmissão é baixa se comparada a outras tecnologias de transmissão sem fio atuais, esta tecnologia também utiliza bandas de frequência livre que não exigem licenciamento para utilização, para cada região estas bandas de frequência livre são diferentes, na Figura 2 está uma ilustração demonstrando a alocação de frequência de algumas bandas de uso livre utilizadas para rádio LoRa:

Alocação de Frequências LoRa 65 MHz AU915 **AS923 US915** Frequência 895,5 902 863 873 915 928 (MHz)

Figura 2: Alocação de Frequências Rádio LoRa

Fonte: National Telecommunications and Information Administration, United States Frequency Allocation Chart. 2016 Disponível em: <a href="https://www.ntia.gov/page/united-states-frequency-allocation-chart">https://www.ntia.gov/page/united-states-frequency-allocation-chart</a> Acesso em 06/07/2025, lora-alliance.org, RP002-1.0.3 LoRaWAN Regional Parameters. Disponível em: <a href="https://lora-alliance.org/wp-content/uploads/2021/05/RP-2-1.0.3.pdf">https://lora-alliance.org/wp-content/uploads/2021/05/RP-2-1.0.3.pdf</a>> Acesso em 06/07/2025

Conforme as alocações demonstradas na Figura 2, a banda EU868 é utilizada na União Europeia, a US915 nos Estados Unidos e as bandas AU915 e AS923 na América do Sul e Ásia respectivamente, tendo em mente as bandas citadas acima foi proposto que o amplificador deste trabalho pudesse operar com todas as bandas citadas, com base nestes requisitos foi determinada uma frequência central de 895,5

MHz e uma largura de banda de 65 MHz de forma a atender todos estes padrões.

#### 1.4 PDK Utilizado

Para o desenvolvimento de circuitos integrados utilizando o software Cadence Virtuoso é necessário um PDK de fabricante, este PDK possui informações sobre os componentes passivos e ativos que podem ser fabricados utilizando a tecnologia de litografia do PDK, para este projeto foi utilizado um PDK de tecnologia de 130 nm da Global Foundries chamado CMRF8SF de 2001, apesar de ser um PDK voltado para desenvolvimento de circuitos de RF este PDK utiliza tecnologia CMOS que é a mais dominante do mercado devido ao custo relativamente baixo de produção se comparado a outras disponíveis e sua alta frequência de chaveamento alta na região de saturação, estas características a tornam dominante no mercado devido a sua utilização em larga escala em circuitos digitais. Este tipo de tecnologia não é considerada a melhor para desenvolvimento de circuitos de RF devido a menor frequência de chaveamento em região ativa e maior figura de ruído se comparado a tecnologias Bi-CMOS que são as mais indicadas para este tipo de circuito apesar de ter um custo de produção mais elevado, apesar destas mazelas a tecnologia foi escolhida pela sua disponibilidade e por ser adequada ao projeto, já que para a frequência central e requisitos escolhidos uma tecnologia CMOS 130 nm é adequada para o projeto, além disso apesar de ser uma tecnologia de 2001 ela ainda é fabricada, sendo assim relevante para os objetivos do trabalho.

### 2 FUNDAMENTOS TEÓRICOS

Neste capítulo será realizada a revisão bibliográfica e análise das topologias encontradas para o projeto de um LNA e serão demonstradas equações úteis para a realização do projeto com base no que foi encontrado na revisão bibliográfica.

## 2.1 Topologias

O primeiro passo para a implementação do projeto é a escolha da topologia LNA a ser utilizada, tendo em vista os requisitos do LNA de figura de ruído, ganho, e as possíveis dificuldades para realizar o casamento de impedância de entrada do LNA o número de topologias disponíveis para utilização é limitado, já que ele deve ser casado

com Rs na entrada sem que possua uma carga resistiva igual a  $R_s$ , já que a utilização de cargas resistiva para esta finalidade acarretaria em uma figura de ruído demasiadamente alta devido ao ruído térmico gerado por elementos resistivos. Durante a revisão bibliográfica deste projeto foram encontradas e analisadas as topologias demonstradas nesta seção.

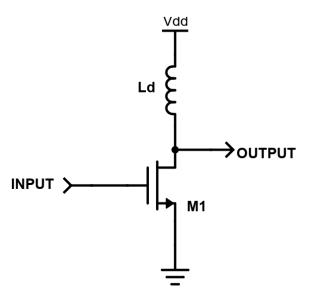

### 2.1.1 Amplificador de Porta Comum com Carga Indutiva

Uma das topologias de LNA encontrada na bibliografia foi o Amplificador de Porta Comum com Carga Indutiva, semelhante a um Amplificador de Porta Comum com Carga Resistiva, porém nesta topologia a carga resistiva é substituída por um indutor que deve ressonar com a capacitância total do circuito no nó de saída, na Figura 3 está um esquemático de um Amplificador de Porta Comum com Carga Indutiva:

Ld E

OUTPUT

W1

NPUT

Figura 3: Esquemático Amplificador Porta Comum com Carga Indutiva

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

O amplificador de porta comum conforme demonstrado na Figura 3 é atrativo para utilização como LNA já que desconsiderando efeitos de modulação de comprimento de canal sua impedância de entrada pode ser expressada como:

Equação 2: Impedância de Entrada Amplificador Porta Comum

$$Z_{in}=rac{1}{g_m}$$

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Nesta expressão o termo Z<sub>in</sub> corresponde a impedância de entrada e g<sub>m</sub> ao ganho de transcondutância do transistor. Como pode se observar isto faz com que a impedância de entrada do circuito possa ser dimensionada variando o valor de g<sub>m</sub> do transistor o que é atrativo do ponto de vista do casamento de impedância de entrada, um dos problemas intrínsecos desta topologia é que sua figura de ruído mínima na condição de casamento é de 3dB o que o torna não atrativo para o projeto proposto devido requisito mínimo estabelecido na seção 1.2 de NF<4dB, além disto esta topologia sofre de efeitos de modulação de comprimento de canal indesejados quando implementado em tecnologias cujo comprimento de canal seja próximo de 100nm a tornando imprópria para a implementação neste projeto, já que o PDK utilizado é de tecnologia 130nm.

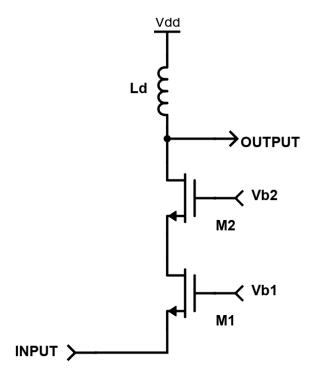

### 2.1.2 Amplificador Cascode de Porta Comum

Esta topologia é similar a topologia explorada na seção anterior, porém na configuração de Cascode, na Figura 4 está demonstrado o esquemático para esta topologia:

Figura 4: Esquemático Amplificador Porta Comum Cascode com Carga Indutiva

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Graças a adição de M2 ao amplificador esta topologia pode ser utilizada com tecnologias de 130nm já que a adição deste segundo transistor faz com que os efeitos de modulação de comprimento de canal sejam minimizados, de forma que mesmo para transistores de comprimento de canal próximo a 100nm, a impedância de entrada ainda seja determinada por:

Equação 3: Impedância de Entrada Amplificador Fonte Comum Cascode

$$Z_{in}=rac{1}{g_m}$$

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Nesta equação assim como na anterior  $Z_{in}$  corresponde a impedância de entrada e  $g_m$  ao ganho de transcondutância do transistor M1. Apesar deste aprimoramento em relação a topologia explorada no capítulo anterior esta topologia têm um ruído adicional

se comparada a anterior devido a adição do transistor M2, além disso ela ainda possui figura de ruído superior a 3db a tornando não atrativa para este projeto.

### 2.1.3 Amplificador de Fonte Comum com Carga Indutiva

Uma das topologias de Fonte Comum para LNAs encontrada na bibliografia foi o Amplificador de Fonte Comum com Carga Indutiva, esta topologia assim como nas demonstradas anteriormente, substitui uma carga resistiva por um indutor, o esquemático para este tipo de amplificador está na Figura 5:

Figura 5: Esquemático Amplificador Fonte Comum com Carga Indutiva

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Para este circuito a impedância de entrada desconsiderando a capacitância entre a porta é dada pela seguinte expressão:

Equação 4: Impedância de Entrada Amplificador Fonte Comum

$$Zin(s) = rac{L_1(C_1 + C_f)s^2 + R_s(C_1 + C_f)s + 1}{[L_1C_1s^2 + (R_sC_1 + g_mL_1)s + 1 + g_mR_s]C_fs}$$

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Nesta equação o termo  $Z_{in}$  corresponde a impedância de entrada do amplificador,  $L_1$  corresponde à indutância do indutor  $L_d$ ,  $C_1$  a capacitância parasita paralela do indutor  $L_d$ ,  $C_f$  a capacitância parasita entre dreno e gate do transistor,  $R_s$  como a impedância da fonte e  $g_m$  o ganho de transcondutância do transistor. De acordo com esta expressão a impedância de entrada do circuito não está isolada da impedância de saída fazendo com que exista um certo grau de complexidade atrelado a realização de projetos utilizando esta topologia, além disto está topologia têm seu ganho limitado em altas frequências devido ao efeito Miller onde a capacitância parasita entre a porta e dreno do transistor age como uma realimentação negativa, isso faz com que o ganho em altas frequências deste tipo de amplificador seja muito limitado. por estes motivos esta topologia é raramente utilizada em projetos modernos.

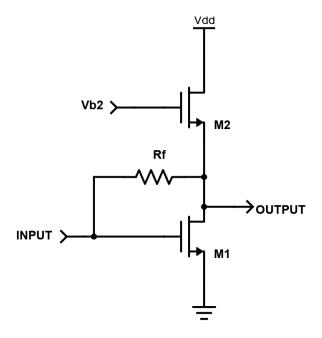

# 2.1.4 Amplificador de Fonte Comum com Realimentação Resistiva

Para esta topologia são utilizados 2 transistores sendo que o transistor M2 atua como uma fonte de corrente e M1 como amplificador, um diferencial desta topologia em relação às demonstradas anteriormente é a ausência de indutores fazendo com que este tipo de circuito ocupe um espaço físico menor se comparado aos demonstrados anteriormente, o esquemático do circuito está demonstrado na Figura 6:

Figura 6: Esquemático Amplificador Fonte Comum com Realimentação Resistiva

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Assim como nos amplificadores de porta comum a impedância de entrada deste circuito é expressa por:

Equação 6: Impedância de Entrada Amplificador Fonte Comum

$$Z_{in}=rac{1}{g_m}$$

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Assim como nos casos anteriores, Zin corresponde a impedância de entrada do circuito e  $g_m$  ao ganho de transcondutância do transistor M1. Fazendo com que a impedância de entrada possa ser dimensionada de acordo com o valor de  $g_m$  do transistor M1. Um dos problemas intrínsecos deste circuito é o ruído adicionado pelo resistor de realimentação e transistor M2, devido a estes fatores a figura de ruído para esta topologia é de no mínimo cerca de 3 dB fazendo com que ela não seja atrativa para utilização neste projeto devido ao requisito mínimo estabelecido na seção 1.2 de NF < 4 dB.

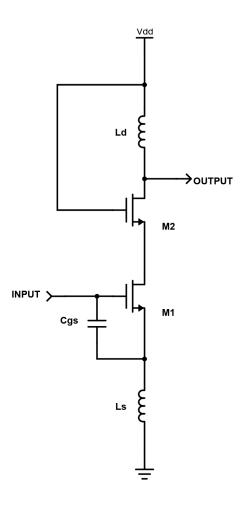

# 2.1.5 Amplificador Cascode Fonte Comum com Degeneração Indutiva

Esta topologia é similar ao Amplificador de Fonte Comum com Carga Indutiva, porém em configuração de Cascode, o esquemático para esta topologia está na Figura 8:

Figura 8: Esquemático Amplificador Cascode Fonte Comum com Degeneração Indutiva

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Por conta da adição do transistor M2 em configuração de Cascode, a impedância de entrada deste circuito possui um bom isolamento da impedância de saída fazendo com que o casamento de impedância de entrada para este tipo de amplificador seja relativamente simples de ser realizado se comparado a um amplificador de Fonte Comum com Carga Indutiva, a adição do transistor M2 em configuração Cascode também minimiza o efeito Miller, fazendo com que a frequência

de operação máxima seja mais alta do que a configuração de Fonte Comum com Carga Indutiva. Para esta topologia a figura de ruído está diretamente atrelada a frequência central do projeto e a frequência de ganho unitário do amplificador, quanto menor for a frequência central e maior a frequência de ganho unitário menor a figura de ruído. Por estes motivos está topologia é amplamente utilizada em designs modernos de amplificadores de radiofrequência.

### 2.1.6 Amplificadores Diferenciais

Considerando todas as topologias anteriormente apresentadas todas elas podem ser implementadas de maneira diferencial, as principais vantagens deste tipo de topologia se comparadas as topologias single ended demonstradas anteriormente é que a distorção de ordem para amplificadores diferenciais é consideravelmente menor. O principal fator que dificulta a implementação deste tipo de circuito no escopo do projeto é o fato que a entrada do circuito é realizada de maneira single ended enquanto que a entrada deste tipo de amplificador é diferencial, isto faz com que seja necessário um transformador Balun para converter o sinal de entrada single ended em um sinal diferencial, este fato faz com que este tipo de circuito não seja atrativo para utilização neste projeto por questões de limitação de tecnologia.

### 2.1.7 Topologia Escolhida

Tendo em consideração os requisitos do projeto, dificuldades de implementação e tempo disponível para realização foi escolhida a topologia Cascode de Fonte Comum com Degeneração Indutiva, nos próximos capítulos esta topologia será analisada de maneira mais aprofundada.

Figura 9: Amplificador Cascode Fonte Comum com Degeneração Indutiva

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

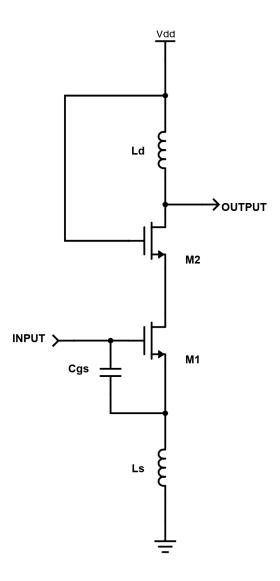

# 2.2 Casamento de Impedância de Entrada para um Cascode Degenerativo

O casamento da impedância de entrada do amplificador com a impedância Rs da fonte é imprescindível para o funcionamento do circuito, tendo em vista a impedância de entrada do circuito é possível verificar se o casamento com Rs na banda de interesse está ocorrendo de forma satisfatória por meio da análise do parâmetro S11, este parâmetro representa a perda de retorno na entrada do amplificador, quanto menor o valor deste parâmetro menor a taxa de reflexão, segundo a bibliografia para uma operação correta do amplificador este parâmetro deve assumir

valores inferiores a -10dB na etapa de simulação para a frequência central. Para a topologia de Cascode com degeneração indutiva escolhida previamente, a impedância de entrada do amplificador é dada pela seção de entrada do amplificador, demonstrada na Figura 10:

INPUT Cgs Ls Ls

Figura 10: Entrada Amplificador Cascode Fonte Comum com Degeneração Indutiva

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Para este circuito, a impedância de entrada pode ser determinada desconsiderando a impedância parasita entre dreno e fonte do transistor, pela seguinte expressão:

Equação 7: Impedância de Entrada Amplificador Fonte Comum Cascode

$$Z_{in} = rac{1}{sC_{gs}} + s(L_g + L_s) + rac{g_m L_s}{C_{gs}}$$

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Nesta equação o termo  $Z_{in}$  corresponde a impedância de entrada do amplificador,  $C_{gs}$  a capacitância entre *gate* e *source* do transistor M1,  $L_g$  a indutância do indutor do *gate* do transistor M1,  $L_s$  a indutância do indutor de *source* e  $g_m$  ao ganho de transcondutância do transistor M1. Nota-se que o quarto termo desta impedância é um valor real

independente da frequência, portanto essa componente pode ser dimensionada para que seja igual a  $R_{s}$ , considerando apenas a capacitância  $C_{gs}$  intrínseca do transistor o valor do indutor  $L_s$  para que o quarto termo seja igual a um  $R_s$  de  $50\Omega$  é muito pequeno para que o casamento possa ser realizado com os indutores disponíveis no PDK, portanto é utilizado um capacitor em paralelo a porta e a fonte transistor M1, aumentando o valor de C<sub>gs</sub> para que por consequência L<sub>s</sub> possa assumir valores que possam ser implementados em um circuito real, o valor da capacitância C<sub>qs</sub> também afeta diretamente a largura de banda do amplificador e a frequência de ganho unitário, com valores maiores possuindo uma largura de banda maior e uma maior figura de ruído por consequência. Depois de dimensionados L<sub>s</sub> e C<sub>qs</sub> para que a componente real da impedância de entrada seja igual a impedância R<sub>s</sub> da fonte, é necessário que a componente imaginária da impedância de entrada do circuito seja nula na frequência central da banda para que a impedância de entrada do circuito esteja casada com Rs nesta frequência, para isso o indutor  $L_{\rm g}$  é então dimensionado de forma que a soma de  $L_{\rm g}$  e  $L_{\rm s}$  entre em ressonância com a componente capacitiva da impedância de entrada na frequência central de interesse. Esse indutor geralmente assume valores demasiadamente altos para ser implementado de forma integrada então em primeiro plano será considerado que o indutor L<sub>a</sub> é implementado de forma externa ao circuito. Com base nisso a frequência de ressonância para fins de dimensionamento de La é expressa por:

Equação 8: Impedância de Entrada Amplificador Fonte Comum Cascode

$$\omega_0 = rac{1}{\sqrt{(L_q + L_s) * C_{qs}}}$$

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Com  $\omega_0$  sendo a frequência de ressonância,  $L_g$  como a indutância do indutor de gate,  $L_s$  como a indutância do indutor de source e  $C_{gs}$  como a capacitância entre gate e source do circuito. Após o dimensionamento correto de  $L_s$ ,  $C_{gs}$  e  $L_g$ , a entrada do amplificador terá uma impedância real igual a  $R_s$  na frequência central  $\omega_0$  fazendo com que ele esteja casado com  $R_s$  na frequência central da banda a ser amplificada, isso pode ser

verificado por meio do parâmetro de reflexão S<sub>11</sub> do amplificador, caso este parâmetro esteja convergindo para valores inferiores a -10dB na frequência central de interesse o amplificador está casado com Rs nesta frequência.

### 2.3 Indutor de Dreno e Casamento de Impedância de Saída

Para um Cascode Fonte Comum com Indução Degenerativa o Indutor  $L_d$  deverá ressonar com a capacitância total do nó de saída, em um receptor completo isto implica que ele deverá ressonar com a soma da capacitância do circuito no nó de saída e a capacitância de entrada do próximo estágio do receptor, como neste trabalho o escopo se limita a seção do LNA a impedância de saída do amplificador deverá estar casado em  $R_s$ =50 $\Omega$ , para que o coeficiente de transmissão direta  $S_{21}$  seja medido na porta de saída de maneira adequada, o casamento de impedância da saída do circuito pode ser realizado com associações de componentes passivos.

### 2.4 Figura de ruído

A figura de ruído de um amplificador é o ruído introduzido ao sinal devido a este estágio de amplificação. A figura de ruído de um Cascode de Indução Degenerativa quando a entrada do amplificador está na frequência de ressonância e sua impedância está casada com a impedância Rs da fonte é segundo Razavi:

Equação 9: Figura de Ruído Amplificador Fonte Comum Cascode

$$NF = 1 + g_m * Rs * \gamma * (rac{\omega_0}{\omega_t})^2$$

Fonte: Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

Nesta equação NF corresponde à figura de ruído do amplificador, gm o ganho de transcondutância do amplificador,  $R_s$  a impedância da fonte de entrada,  $\gamma$  como um coeficiente determinado pelas características do substrato utilizado para a fabricação do transistor,  $\omega_0$  a frequência central do amplificador e  $\omega_t$  como a frequência de ganho unitário do amplificador. Segundo esta expressão a figura de ruído deste circuito é

diretamente proporcional ao ganho de transcondutância e dependente da relação entre a frequência de ressonância  $\omega_0$  e a frequência de ganho unitário  $\omega_t$ , sendo que esta frequência de ganho unitário pode ser determinada segundo Saad pela relação:

Equação 10: Impedância de Entrada Amplificador Fonte Comum Cascode

$$\omega_t = rac{g_m}{C_{gd}*C_{gs}}$$

Fonte: Sehmi Saad, Fayrouz. Haddad, Aymen Ben Hammadi. Impact of multi-finger MOSFET geometry on the electrical performance of RF circuits. Microelectronics Reliability, 2022, 129

Nesta equação  $g_m$  corresponde ao ganho de transcondutância do transistor,  $C_{gd}$  a capacitância intrínseca entre *gate* e *drain* do transistor e  $C_{gs}$  a capacitância intrínseca entre *gate* e *source* do transistor. Disso podemos concluir que a figura de ruído é diretamente proporcional a largura de banda do circuito que é determinada pelo valor de  $C_{gs}$  e também ao ganho de transcondutância  $g_m$ , fazendo com que circuitos com uma maior largura de banda e um maior ganho sejam intrinsecamente mais ruidosos

Uma das maneiras de reduzir o ruído intrínseco dos transistores utilizados no projeto é a utilização de múltiplos dedos (*fingers*), segundo a bibliografia utilizada o ruído mínimo de um transistor de tecnologia NMOS é dado pela expressão:

#### Equação 11: Impedância de Entrada Amplificador Fonte Comum Cascode

$$NF_{min} = 1 + K_f * rac{\omega_{max}}{\omega_t} * \sqrt{(R_d + R_g) * g_m}$$

Fonte: Sehmi Saad, Fayrouz. Haddad, Aymen Ben Hammadi. Impact of multi-finger MOSFET geometry on the electrical performance of RF circuits. Microelectronics Reliability, 2022, 129

Sendo  $K_f$  o coeficiente de Fukui,  $\omega_{max}$  a frequência de ganho de potência unitária,  $R_d$  a resistência de substrato e  $R_g$  a resistência de porta do transistor que pode ser modelada pela seguinte expressão:

Equação 12: Impedância de Entrada Amplificador Fonte Comum Cascode

$$R_g \cong R_{sch} * rac{W}{L} * rac{1}{3*N_{con}^2*N_f}$$

Fonte: Sehmi Saad, Fayrouz. Haddad, Aymen Ben Hammadi. Impact of multi-finger MOSFET geometry on the electrical performance of RF circuits. Microelectronics Reliability, 2022, 129

Sendo  $N_f$  o número de dedos,  $R_{sch}$  a resistência da camada da porta do transistor, W a largura do transistor, L o comprimento do transistor e  $N_{con}$  o número de conectores utilizados para o transistor podendo assumir os valores 1 ou 2, consequentemente um aumento do número de dedos sem que a relação W/L seja modificada resulta numa diminuição da resistência de porta do transistor que por fim resulta numa diminuição da figura de ruído do transistor, segundo a bibliografia um aumento no número de dedos melhora de forma significativa as características de figura de ruído do transistor para até 10 dedos após este ponto a diminuição de  $NF_{min}$  começa a se tornar cada vez menor a ponto de ser negligenciável para transistores com mais de 20 dedos.

## 3 SIMULAÇÃO UTILIZANDO COMPONENTES IDEAIS

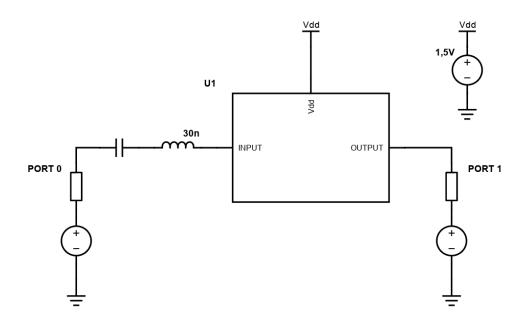

Para a implementação do circuito primeiramente é realizado um projeto utilizando modelos de simulação de transistores RF disponíveis no software Cadence Virtuoso na tecnologia CMR8SF, em conjunto com modelos de simulação de componentes ideias de forma a determinar a viabilidade inicial do circuito.

## 3.1 Esquemático de Simulação

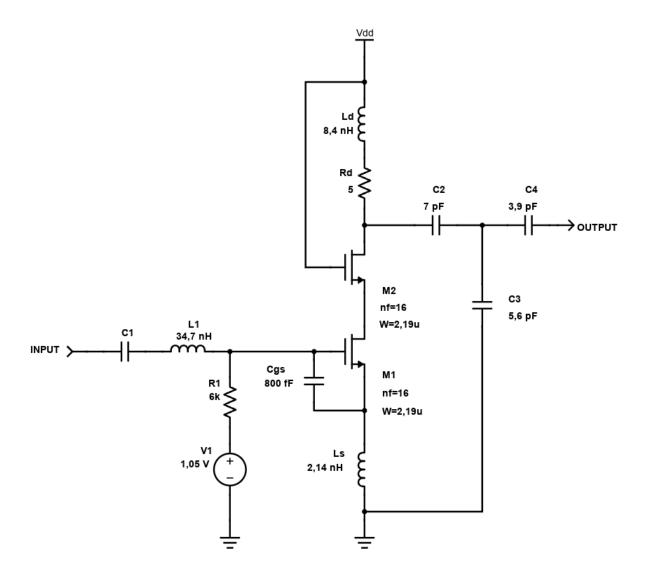

Esta iteração do projeto foi realizada utilizando transistores NFET RF da biblioteca CMRF8SF com 16 dedos em conjunto com componentes ideais da biblioteca Analoglib, utilizando as expressões e embasamento teórico demonstrados anteriormente para realizar o dimensionamento dos componentes utilizados, foi obtido o seguinte esquemático:

Figura 11: Esquemático Amplificador Componentes Ideais

Como pode ser visto na imagem a largura W escolhida para os transistores foi de 2,19µm por dedo, com um valor total de 35,04µm, o valor do capacitor paralelo  $C_{\rm gs}$  foi de 800fF, Ls de 2,14nH,  $L_{\rm g}$  igual a 34,75nH e  $L_{\rm d}$  igual a 8,4nH em série com um resistor de 5 $\Omega$  para simular a resistência parasita série de um indutor real de forma a se obter um ganho mais realista para o circuito, para a polarização foi utilizada uma fonte de tensão ideal de 1,05V ligada a porta por um resistor de 6k $\Omega$ , também foi adicionado o capacitor de desacoplamento C8 na entrada, na saída do circuito foi utilizado um circuito de transformação de impedâncias projetado utilizando carta de Smith para que as medições na porta PORT1 sejam realizadas de maneira correta.

### 3.2 Resultados de Simulação

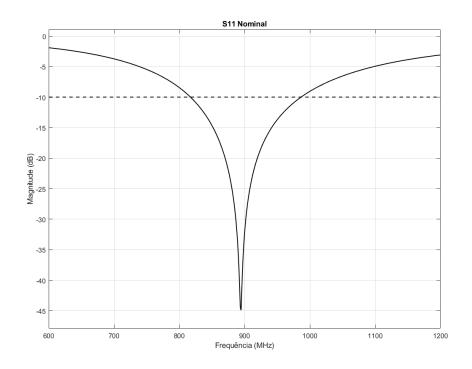

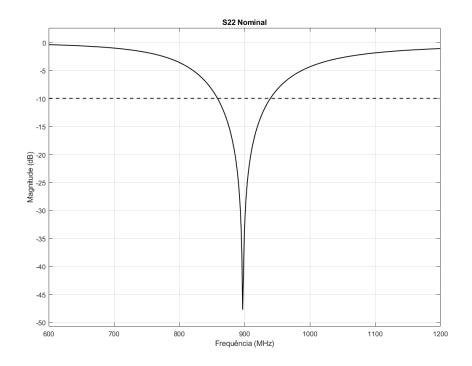

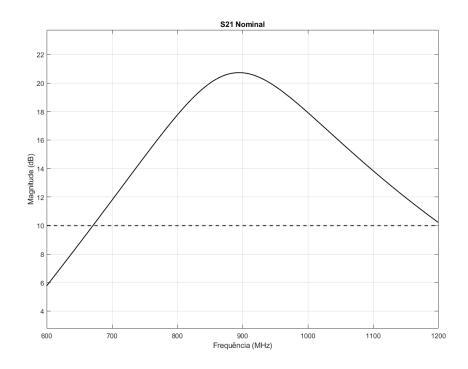

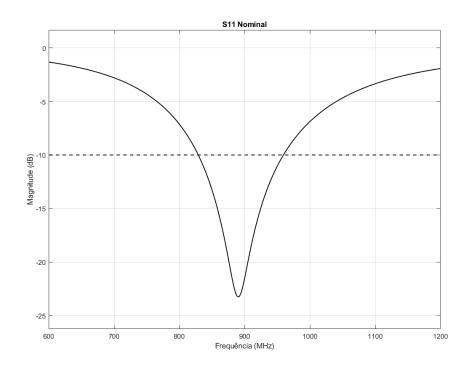

Para verificar a viabilidade inicial do circuito foram realizadas simulações de parâmetro S de  $S_{11}$ ,  $S_{22}$ ,  $S_{21}$ , NF e dos coeficientes de estabilidade Mu e Kf, para os parâmetros  $S_{11}$  e  $S_{22}$  quanto menor for o resultado em dB na frequência central menor a taxa de reflexão, consequente o circuito então possui uma melhor performance quanto menor forem esses valores na frequência central, para o parâmetro  $S_{21}$  quanto maior for o valor em dB na frequência central melhor a performance do circuito visto que quanto o ganho do circuito melhor o amplificador é, para NF quanto menor o valor em dB melhor a performance do circuito visto que quanto menor a figura de ruído melhor a performance do circuito, já para Mu quanto maior o valor menos suscetível o circuito é a oscilações, nas figuras a seguir estão os resultados de simulação, as linhas tracejadas em preto representam os pontos de requisito mínimo definidos na seção 1.2:

Figura 11: Parâmetro S<sub>11</sub> Amplificador com Componentes Ideais

Figura 13: Parâmetro S<sub>22</sub> Amplificador com Componentes Ideais

Figura 14: Parâmetro  $S_{21}$  Amplificador com Componentes Ideais

Figura 15: Figura de Ruído Amplificador com Componentes Ideais

Figura 16: Fator Kf Amplificador com Componentes Ideais

Como pode se observar o amplificador possui um comportamento inicial adequado em referência aos requisitos mínimos de projeto, o amplificador também é estável na banda de interesse visto que Kf e Mu ambos possuem valor superior a 1 na banda. Como haverá uma degradação na performance ao utilizar componentes reais e na etapa de layout o resultados de ganho  $S_{21}$  pode ser insuficiente, na Tabela 1 estão os valores de  $S_{11}$ ,  $S_{22}$ ,  $S_{21}$  e NF na frequência central:

Tabela 1: Resultados de Simulação Amplificador com Componentes Ideais

| S <sub>11</sub> | S <sub>22</sub> | S <sub>21</sub> | NF    |

|-----------------|-----------------|-----------------|-------|

| -45,5dB         | -27,1dB         | 14,8dB          | 1,5dB |

## 4 SIMULAÇÃO UTILIZANDO COMPONENTES REAIS

Nesta etapa foi realizada a implementação do circuito proposto utilizando componentes passivos da tecnologia CMRF8SF, em conjunto com os transistores de RF utilizados na etapa anterior, além disso houve alterações no circuito de forma a melhorar seu desempenho, estas alterações serão exploradas nas seções seguintes deste tópico.

### 4.1 Alterações do Circuito:

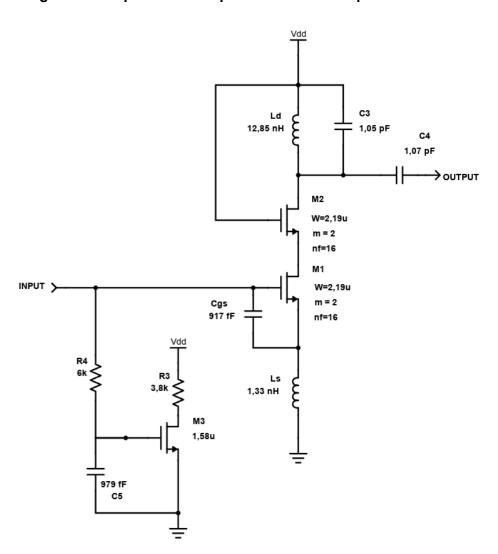

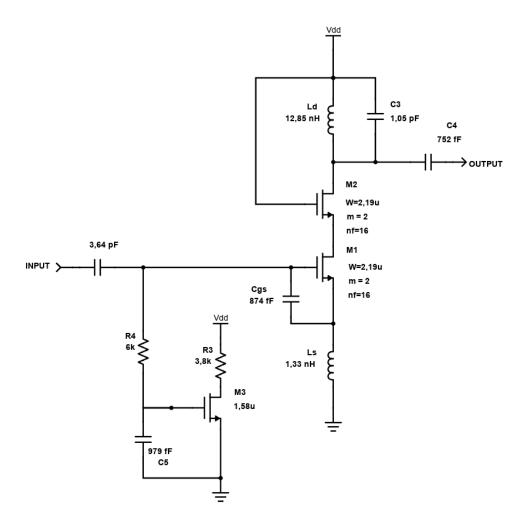

Nesta versão do circuito foram utilizados transistores de RF iguais aos da etapa anterior com W=35.04µ porém com multiplicidade 2 para os transistores da parte ativa do circuito, esta alteração foi realizada já que ao utilizar transistores em paralelo se obtém uma figura de ruído menor e um ganho S<sub>21</sub> maior se comparado a um único transistor, o circuito de polarização nesta etapa foi implementado por meio de um espelho de corrente simples, a condição de polarização também foi revisada de forma que o amplificador esteja no ponto de polarização com o maior ganho possível. Os componentes passivos responsáveis pelo casamento de entrada também foram redimensionados, primeiro foi selecionado um indutor com um valor próximo do menor valor possível da tecnologia, esta decisão foi realizada para minimizar área do layout e a figura de ruído do circuito, pois além de um indutor menor possuir uma resistência parasita menor ele também irá incorrer em um capacitor C<sub>os</sub> paralelo a porta e fonte do transistor de entrada com uma capacitância menor para a condição de casamento escolhida, estes dois fatores fazem com que a figura de ruído total do circuito seja menor. Por fim, o indutor de dreno foi redimensionado de forma que o ganho S<sub>21</sub> do amplificador seja maximizado, o circuito de casamento na saída também foi modificado para que sejam utilizados apenas 2 capacitores com valores compatíveis com os que podem ser fabricados na tecnologia utilizada. Também foram adicionados pads na entrada e saída do circuito, estes pads introduzem parasitas e devem ser considerados no casamento de impedâncias. O capacitor de desacoplamento na entrada e o indutor de porta nesta etapa do circuito ainda estão implementados de forma ideal visto que o capacitor é utilizado apenas para desacoplamento e o indutor neste caso é implementado de forma externa. Os capacitores utilizados foram do tipo MIM (Metal Insulator Metal), este tipo de capacitor apresenta uma boa capacitância por área, poucos parasitas, boa linearidade e estabilidade os tornando propícios para utilização em circuitos integrados de RF, os indutores por sua vez são indutores padrões da tecnologia com plano de terra em BFMOAT visto que este plano de terra oferece um fator de qualidade e frequência de ressonância maior do que o plano de terra M1, na Figura 18 está o esquemático do circuito:

Figura 18: Esquemático Amplificador com Componentes Reais

## 4.2 Esquemático de Simulação:

Utilizando o circuito proposto no esquemático anterior foi criado um esquemático de simulação no software para verificar o comportamento do circuito, na Figura 19 está o esquemático:

Figura 19: Esquemático de Simulação Amplificador com Componentes Reais

Nota-se que o esquemático de simulação possui os elementos passivos que são utilizados de forma off-chip visto que o bloco do amplificador deve conter apenas os componentes integrados.

## 4.3 Resultados de Simulação:

Utilizando uma simulação de parâmetro S do circuito foram realizadas as simulações de  $S_{11}$ ,  $S_{22}$ ,  $S_{21}$ , NF e dos coeficientes de estabilidade Mu e Kf, a seguir estão os resultados de simulação:

Figura 20: Parâmetro S<sub>11</sub> Amplificador com Componentes Reais

Figura 21: Parâmetro S<sub>22</sub> Amplificador com Componentes Reais

Figura 22: Parâmetro  $S_{21}$  Amplificador com Componentes Reais

Figura 23: Figura de Ruído Amplificador com Componentes Reais

Figura 24: Fator Kf Amplificador com Componentes Reais

Figura 25: Fator Mu Amplificador com Componentes Reais

Com base nos resultados de simulação podemos dizer que as entradas e saída estão casados corretamente, pois  $S_{11}$  e  $S_{22}$  convergem para -45dB na frequência central, o ganho está em um nível bom pois está superior a 20dB na frequência central, a figura de ruído também está em um nível bom, estando próxima a 1dB na frequência central, por último o amplificador é estável visto que ambos os coeficientes de estabilidade Kf e Mu possuem valores superiores a 1 na banda, na Tabela 2 estão valores de  $S_{11}$ ,  $S_{22}$ ,  $S_{21}$  e NF na frequência central:

Tabela 2: Resultados de Simulação Amplificador com Componentes Reais

| S <sub>11</sub> | S <sub>22</sub> | S <sub>21</sub> | NF    |

|-----------------|-----------------|-----------------|-------|

| -42,2dB         | -36,3dB         | 20,7dB          | 1,1dB |

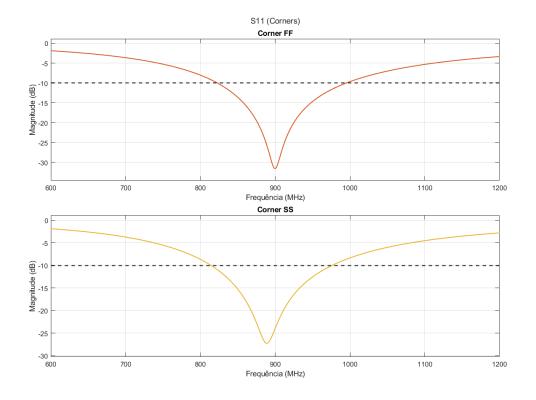

#### 4.4 Simulação de Corners:

Para verificar se o circuito está apto a ser fabricado é necessário que este seja testado com simulações de variação de processo para garantir um funcionamento robusto, uma das simulações de desvio de processo utilizada na indústria é a simulação de corners, esta que simula situações extremas de processo de fabricação, geralmente uma simulação de corners contém 4 corners sendo estes FF (*Fast Fast*), FS (*Fast Slow*), SF (*Slow Fast*) e SS (*Slow Slow*), estes corners se referem a 4 extremos de fabricação com FF sendo o melhor caso possível e SS sendo o pior caso possível, os corners têm as seguintes características de acordo com a Tabela 3:

**Tabela 3: Características dos Corners Utilizados**

| CORNER | NMOS                                 | PMOS                                 |

|--------|--------------------------------------|--------------------------------------|

| FF     | Baixa Resistência<br>Alta Mobilidade | Baixa Resistência<br>Alta Mobilidade |

| FS     | Baixa Resistência<br>Alta Mobilidade | Alta Resistência<br>Baixa Mobilidade |

| SF     | Alta Resistência<br>Baixa Mobilidade | Baixa Resistência<br>Alta Mobilidade |

| SS     | Alta Resistência<br>Baixa Mobilidade | Alta Resistência<br>Baixa Mobilidade |

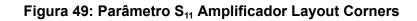

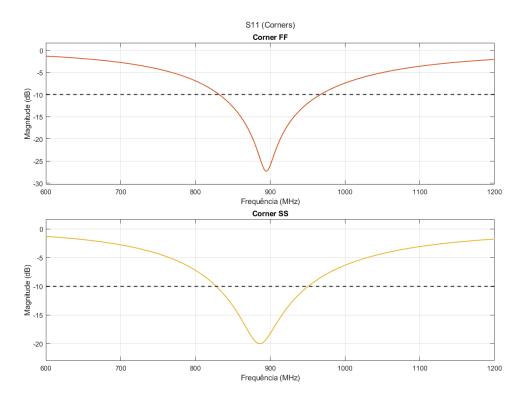

Como no circuito proposto somente foram utilizados transistores do tipo NMOS foram feitas somente simulações dos tipos FF e SS, a seguir estão os resultados da simulação de corners do circuito:

Figura 26: Parâmetro S<sub>11</sub> Amplificador com Componentes Reais Corners

Figura 27: Parâmetro S<sub>22</sub> Amplificador com Componentes Reais Corners

Figura 28: Parâmetro S<sub>21</sub> Amplificador com Componentes Reais Corners

Figura 29: Figura de Ruído Amplificador com Componentes Reais Corners

Figura 30: Fator Kf Amplificador com Componentes Reais Corners

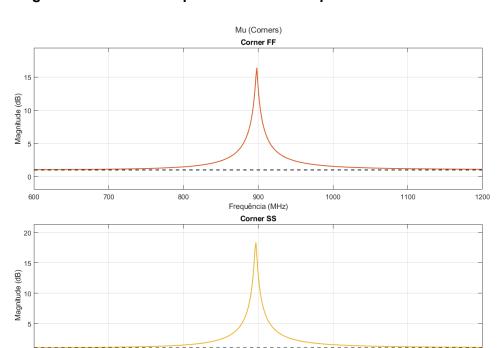

Figura 31: Fator Mu Amplificador com Componentes Reais Corners

Como se pode ver pelos resultados apresentados o circuito ainda responde como esperado em todos os corners simulados, porém com uma pequena degradação nos corners SF e SS visto que os transistores utilizados para a amplificação do sinal são ambos do tipo NMOS, na Tabela 4 estão os valores obtidos na frequência central para os 4 corners simulados:

900

Frequência (MHz)

600

700

Tabela 4: Resultados de Simulação de Corners Amplificador com Componentes Reais

| Corner | S <sub>11</sub> | S <sub>22</sub> | S <sub>21</sub> | NF    |

|--------|-----------------|-----------------|-----------------|-------|

| FF     | -30dB           | -34,3dB         | 21,1dB          | 1dB   |

| SS     | -25,8dB         | -38,7dB         | 20,2dB          | 1,1dB |

Como pode se observar por meio da Tabela 4 os resultados para ambos os Corners foram satisfatórios dados os requisitos mínimos definidos.

1200

#### 4.5 Simulação de Monte Carlo:

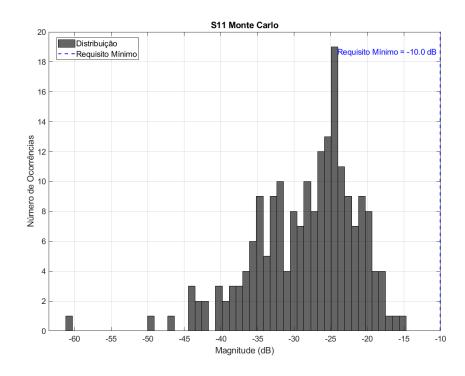

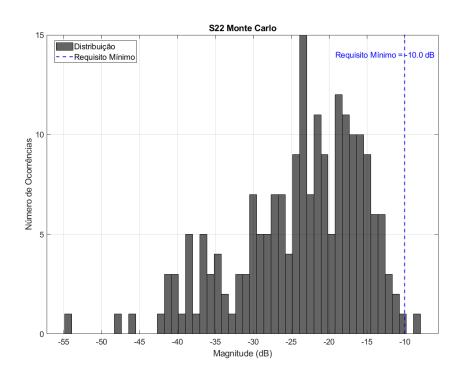

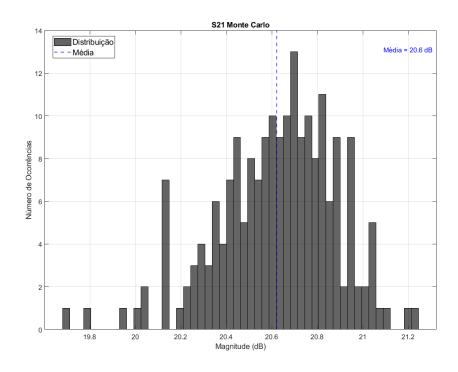

Assim como a simulação anterior esta etapa visa verificar como o circuito responde a desvios de processo de fabricação esperados. Para isso é utilizada uma simulação utilizando o Método de Monte Carlo. Neste tipo de simulação são utilizados dados de distribuição dos parâmetros dos componentes da tecnologia que são fornecidos pelo fabricante responsável pelo PDK. Com estes dados são realizadas diversas simulações onde os parâmetros dos componentes são modificados de forma aleatória dentro dos limites estatísticos esperados segundo a distribuição fornecida pelo PDK para cada componente. Cada simulação representa uma possível variação do circuito após a fabricação, refletindo o impacto dos desvios esperados do processo de produção. O objetivo é verificar a partir dos resultados dessas simulações a quantidade de circuitos que se mantêm dentro da faixa de operação especificada e analisar a robustez do projeto frente às variações esperadas do processo de fabricação. Para este circuito foram realizadas 200 simulações na frequência central, com um intervalo de confiança de 95%. Os histogramas com as distribuições de cada parâmetro estão nas figuras a seguir:

Figura 32: Parâmetro S<sub>11</sub> Amplificador com Componentes Reais Monte Carlo

Figura 33: Parâmetro  $S_{22}$  Amplificador com Componentes Reais Monte Carlo

Figura 34: Parâmetro S<sub>21</sub> Amplificador com Componentes Reais Monte Carlo

Figura 35: Figura de Ruído Amplificador com Componentes Reais Monte Carlo

Figura 36: Fator Mu Amplificador com Componentes Reais Monte Carlo

Figura 37: Fator Mu Amplificador com Componentes Reais Monte Carlo

Com base nos resultados de simulação obtidos é possível afirmar que o circuito possui uma boa resistência à variação de processos, com 99,5% das amostras dentro dos requisitos estabelecidos para o projeto com um intervalo de confiança de 95%.

# 5 LAYOUT E SIMULAÇÃO COM EXTRAÇÃO DE PARASITAS

A partir do esquemático demonstrado na seção anterior foi gerado um layout utilizando a ferramenta Layout XL do software, utilizando o circuito extraído a partir do layout foram refeitas as simulações para verificar o comportamento do circuito implementado de forma final. A seguir estão as imagens do Layout do Circuito e os resultados da simulação utilizando o circuito extraído do layout.

### 5.1 Alterações do Circuito:

Nesta iteração do circuito foi adicionado um capacitor de desacoplamento interno de tecnologia MIM interno ao circuito, o modelo de simulação do indutor externo do circuito estava sendo o de um indutor ideal até esta etapa, foi trocado por um modelo de arquivo S2P de um indutor de RF real, modelo LQW18AS33NG00# da Murata Manufacturing Co. , utilizando um arquivo S2P é possível obter resultados de simulação mais realistas já que ele é modelado a partir de um indutor real contendo os parasitas e não linearidades esperados de um indutor de RF. Devido a estas duas alterações, somadas às resistências e capacitâncias parasitas introduzidas no estágio de layout, os valores dos capacitores e indutores de casamento tiveram de ser revisados para se obter uma condição de casamento e performance do circuito semelhante a do estágio anterior, a seguir está o esquemático do circuito utilizado para o layout:

Figura 38: Esquemático Amplificador Layout

# 5.2 Layout da Parte Ativa:

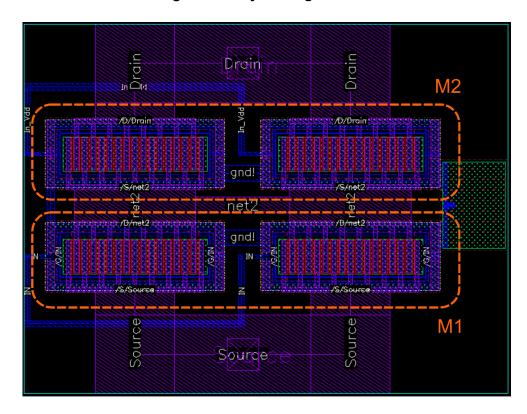

Um dos procedimentos padrões da indústria de microchip durante o desenvolvimento de layout é a criação de um layout separado para a parte ativa do circuito, na Figura 39 está o Layout da Parte Ativa do amplificador proposto contendo os transistores M1 e M2:

Figura 39: Layout Região Ativa

Como pode se ver na imagem todos os transistores seguem a mesma orientação espacial, isto é feito de forma a reduzir variações por desvio de processo de fabricação no estágio de layout sendo esta uma boa prática de layout, visto que caso ocorra uma variação no processo de fabricação todos os transistores irão variar de forma homogênea.

# 5.3 Layout Completo:

Utilizando o Layout da parte ativa demonstrado na Figura 39 foi criado um layout incorporando a parte ativa do circuito, os componentes passivos e a seção de polarização do circuito, na Figura 40 está o Layout completo do circuito:

Area Total:

0,79mm²

Pad DC

Pads Output

Pads Output

Figura 40: Layout Amplificador Completo

Como se pode observar pela Figura 40 a área total do circuito foi de 0,79mm² sendo que os indutores e pads ocupam a maior parte do espaço físico do circuito. O layout foi feito de forma que a distância do pad de entrada e a entrada da região ativa do circuito fosse a menor possível, isso é feito para minimizar o ruído gerado pelas resistências parasitas das trilhas que ligam estes dois pontos e é considerada uma boa prática de layout para este tipo de projeto, também foram utilizadas trilhas grossas nos metais de camadas mais altas do circuito para a trilha de entrada, já que possuem menos parasitas, estes detalhes são cruciais nesta seção do circuito pois a maior parte do ruído introduzido no estágio de layout é devido a esta trilha. Os indutores Ld e Ls foram posicionados no layout de forma que eles estivessem próximos do pad de Vdd e de um

barramento de terra respectivamente, isto foi feito para reduzir resistências e capacitâncias parasitas devido às trilhas o que incorre num descasamento de impedância na entrada e saída do circuito. As trilhas onde passam sinais de alta corrente foram dimensionadas para serem do maior tamanho permitido pela tecnologia e posicionadas de forma que outras trilhas mesmo que de camadas diferentes, o que também é considerada uma boa prática de layout segundo Christopher Saint.

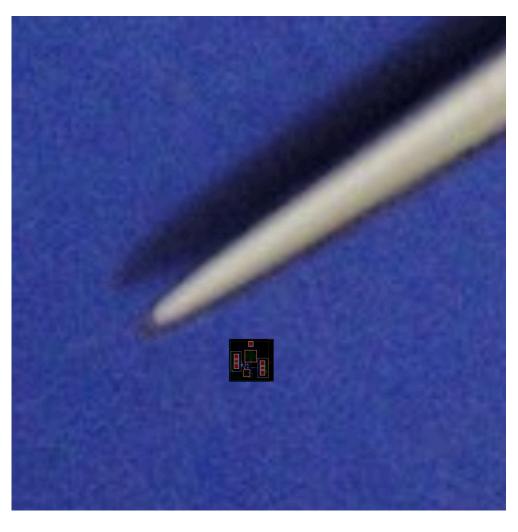

Para se ter uma melhor noção do tamanho do circuito foi feita uma imagem para comparar a dimensão física do circuito com uma ponta de uma agulha, a imagem está representada na Figura 41 a seguir:

Figura 41: Comparação Ilustrativa do Circuito

Fonte: Thamizhpparithi Maari - Obra do próprio, CC BY-SA 3.0

### 5.4 Esquemático de Simulação:

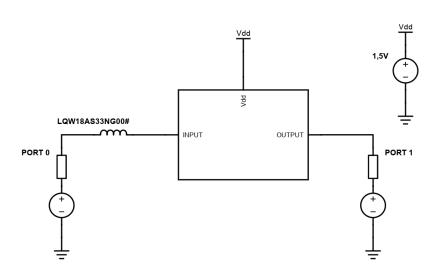

Utilizando o bloco com o circuito equivalente extraído a partir do layout demonstrado na figura 40 foi feito um esquemático de simulação para verificar o comportamento do circuito, na Figura 42 está o esquemático de simulação utilizado nesta etapa:

Figura 42: Esquemático de Simulação Amplificador Layout

Como se pode notar na imagem o modelo de indutor utilizado neste passo foi o de um indutor de RF comercial da Murata Electronics, isto foi feito para se obter uma representação mais realista da performance do circuito e da condição de casamento da entrada, visto que indutores reais de valores próximos a 30nH possuem um comportamento não linear na banda de interesse o que pode acarretar um descasamento na entrada.

### 5.5 Resultados de Simulação:

Utilizando o esquemático demonstrado na Figura 42 foram realizadas simulações de parâmetro  $S_{11}$ ,  $S_{22}$ ,  $S_{21}$ , figura de ruído e fatores de estabilidade Mu e Kf assim como na etapa anterior, nas figuras a seguir estão os resultados de simulação:

Figura 43: Parâmetro S<sub>11</sub> Amplificador Layout

Figura 44: Parâmetro  $S_{22}$  Amplificador Layout

Figura 45: Parâmetro S<sub>21</sub> Amplificador Layout

Figura 46: Figura de Ruído Amplificador Layout

Figura 47: Fator Kf Amplificador Layout

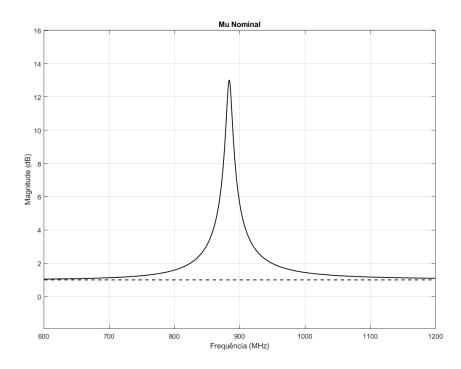

Figura 48: Fator Mu Amplificador Layout

Como pode se observar por meio das figuras acima o circuito sofreu uma degradação de performance se comparado aos resultados da etapa anterior, isto é esperado visto que a etapa de layout introduz parasitas indesejados ao circuito além do capacitor de desacoplamento interno que foi adicionado nesta etapa, o consumo de potência do amplificador foi de 21,45mW o que é dentro do esperado para um circuito deste tipo. Na Tabela 5 estão os valores de  $S_{11}$ ,  $S_{22}$ ,  $S_{21}$  e NF nominais na frequência central em comparação com os resultados obtidos na etapa anterior:

Tabela 5: Comparativo de Resultados de Simulação Esquemático/Layout

| Parâmetro       | Layout  | Esquemático |

|-----------------|---------|-------------|

| S <sub>11</sub> | -22,7dB | -42,2dB     |

| S <sub>22</sub> | -20,1dB | -36,3dB     |

| S <sub>21</sub> | 19,4dB  | 20,7dB      |

| NF              | 1,5dB   | 1,1dB       |

## 5.6 Simulação de Corners:

Assim como na etapa anterior deve se realizar uma simulação de Corners para verificar se o circuito continua com um comportamento adequado em situações extremas de fabricação, foram simulados os Corners FF e SS assim como na etapa anterior, nas figuras a seguir estão os resultados de simulação para os Corners do circuito:

Figura 50: Parâmetro S<sub>22</sub> Amplificador Layout Corners

Figura 52: Figura de Ruído Amplificador Layout Corners

Figura 54: Fator Mu Amplificador Layout Corners

Assim como na etapa anterior o circuito proposto demonstrou ter uma boa resistência a variações de processo de fabricação, obtendo resultados satisfatórios em todos os corners, a seguir está uma tabela com os valores obtidos para os parâmetros do circuito nos 2 corners simulados:

Tabela 6:Resultados de Simulação de Corners Layout

| Corner | S <sub>11</sub> | S <sub>22</sub> | S <sub>21</sub> | NF    |

|--------|-----------------|-----------------|-----------------|-------|

| FF     | -27,3dB         | -20,5dB         | 19,8dB          | 1,5dB |

| SS     | -19,1dB         | -19,7dB         | 18,9dB          | 1,6dB |

### 5.7 Simulação de Monte Carlo:

Como na etapa anterior a simulação de Monte Carlo do circuito também foi refeita utilizando o circuito extraído do Layout proposto, nas figuras a seguir estão os resultados da simulação de Monte Carlo do circuito:

Figura 55: Parâmetro S<sub>11</sub> Amplificador Layout Monte Carlo

Figura 56: Parâmetro S<sub>22</sub> Amplificador Layout Monte Carlo

Figura 57: Parâmetro S<sub>21</sub> Amplificador Layout Monte Carlo

Figura 58: Figura de Ruído Amplificador Layout Monte Carlo

Figura 60: Fator Mu Amplificador Layout Monte Carlo

Com base nos resultados de simulação apresentados é possível afirmar que o circuito têm uma boa resistência a variações de processo de fabricação com 99,5% das amostras dentro dos requisitos estabelecidos com um intervalo de confiança de 95%.

#### 6 CONCLUSÃO

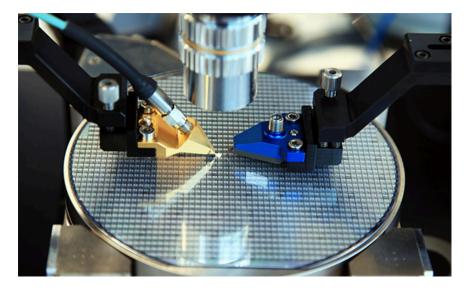

Foi possível desenvolver um LNA com a tecnologia escolhida atendendo os requisitos mínimos com um consumo de potência adequado e com uma boa resistência a variações de processo de fabricação sendo assim viável a sua fabricação. Caso o circuito proposto fosse fabricado ele passaria por testes para verificar seu comportamento, estes testes poderiam ser realizados utilizando um analisador de espectro, para realizar as conexões do circuito ao analisador existem 2 alternativas, a primeira seria enviar o circuito a uma empresa para seu encapsulamento, onde as medições seriam realizadas utilizando o circuito encapsulado, a segunda seria utilizar uma *Wafer Probe* que utiliza ponteiras posicionadas diretamente sobre o circuito integrado, estas ponteiras podem ser conectadas a equipamentos de medição, na figura a seguir está uma imagem de uma *Wafer Probe*:

Figura 61: RF Wafer Probe

Fonte: Vinstronics, Wafer Testing Essentials: The Role of RF Probes. Vinstronics, 2024, Disponível em: <a href="https://vinstronics.com/the-role-of-rf-probes-in-wafer-testing/">https://vinstronics.com/the-role-of-rf-probes-in-wafer-testing/</a>>. Acesso em 06/07/2025

Para verificar se o comportamento do amplificador está comparável a de trabalhos similares este foi comparado a outros trabalhos operando numa frequência similar e usando uma tecnologia compatível com a do projeto, abaixo está uma tabela comparando o LNA proposto neste trabalho com outros LNAs encontrados na bibliografia que operam em frequências similares e com tecnologia comparável à utilizada no projeto:

Tabela 7: Comparativo entre o Amplificador Proposto e os Encontrados na Bibliografia

| Parâmetro                   | Este Trabalho | [3] | [4]     | [5] |

|-----------------------------|---------------|-----|---------|-----|

| S <sub>11</sub> [dB]        | -22,7         | -30 | -10     | -18 |

| S <sub>21</sub> [dB]        | 19,4          | 17  | 23      | 14  |

| NF [dB]                     | 1,5           | 2,2 | 2,5     | 1   |

| Frequência<br>Central [MHz] | 895,5         | 866 | 400-900 | 900 |

| Tecnologia [nm]             | 130           | 130 | 180     | 130 |

Como se pode notar apesar do LNA proposto não ter a melhor figura de ruído e o maior ganho dentre todos os da comparação ele obteve um bom compromisso entre ganho e figura de ruído, obtendo resultados melhores do que o amplificador [3] em ambos os parâmetros, um ganho maior que o amplificador que o amplificador [5] e uma figura de ruído menor do que a do amplificador [4], sendo assim o amplificador proposto neste trabalho possui uma performance equilibrada se comparado a outros similares.

#### 7 BIBLIOGRAFIA UTILIZADA

- [1] Behzad Razavi. RF Microelectronics —2nd ed. EUA: Pearson, 2012.

- [2] Sehmi Saad, Fayrouz. Haddad, Aymen Ben Hammadi. Impact of multi-finger MOSFET geometry on the electrical performance of RF circuits. Microelectronics Reliability, 2022, 129

- [3] Li, Jie & Hasan, s. M. Design and performance analysis of a 866-MHz low-power optimized CMOS LNA for UHF RFID. Industrial Electronics, IEEE Transactions on. 60. 1840-1849. 10.1109/TIE.2012.2190953, 2013

- [4] M. R. Nikbakhsh, E. Abiri, S. Salem and H. Ghasemian, "A power-efficient high gain differential LNA in 0.18µm CMOS technology for 400–900 MHz frequency range, 2017 Iranian Conference on Electrical Engineering (ICEE), 2017

- [5] A. Thakur and S. Chatterjee, "A 4.4-mA ESD-Safe 900-MHz LNA With 0.9-dB Noise Figure," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 29, no. 2, pp. 297-306, Feb. 2021

- [6] Christopher Saint and Judy Saint. IC Mask Design: Essential Layout Techniques (McGraw-Hill, 2002)

- [7] J.D. Kraus, Radio Astronomy, McGraw-Hill, 1966.

- [8] Vinstronics, Wafer Testing Essentials: The Role of RF Probes. Vinstronics, 2024, Disponível em: <a href="https://vinstronics.com/the-role-of-rf-probes-in-wafer-testing/">https://vinstronics.com/the-role-of-rf-probes-in-wafer-testing/</a>>. Acesso em 06/07/2025

- [8] National Telecommunications and Information Administration, United States Frequency Allocation Chart. 2016 Disponível em: <a href="https://www.ntia.gov/page/united-states-frequency-allocation-chart">https://www.ntia.gov/page/united-states-frequency-allocation-chart</a> Acesso em 06/07/2025

- [9] lora-alliance.org, RP002-1.0.3 LoRaWAN Regional Parameters. Disponível em: <a href="https://lora-alliance.org/wp-content/uploads/2021/05/RP-2-1.0.3.pdf">https://lora-alliance.org/wp-content/uploads/2021/05/RP-2-1.0.3.pdf</a> Acesso em 06/07/2025