## UNIVERSIDADE FEDERAL DO PARANÁ

EDUARDO LUIZ SOPPA

# SISTEMA TOLERANTE A FALHAS UTILIZANDO WINDOWS CE, FOCANDO CONTROLADORES INDUSTRIAIS

CURITIBA 2009

## **EDUARDO LUIZ SOPPA**

# SISTEMA TOLERANTE A FALHAS UTILIZANDO WINDOWS CE, FOCANDO CONTROLADORES INDUSTRIAIS

Dissertação apresentada como requisito parcial à obtenção do grau de Mestre em Engenharia Elétrica, Programa de Pós-Graduação em Engenharia Elétrica, Departamento de Engenharia Elétrica, Setor de Tecnologia, Universidade Federal do Paraná.

Orientador: Prof. José Manoel Fernandes, Ph.D.

CURITIBA

## TERMO DE APROVAÇÃO

## EDUARDO LUIZ SOPPA

## SISTEMA TOLERANTE A FALHAS UTILIZANDO WINDOWS CE, FOCANDO CONTROLADORES INDUSTRIAIS

Dissertação aprovada como requisito parcial para a obtenção do grau de Mestre no Curso de Pos-Graduação em Engenharia Elétrica, Setor de Tecnologia da Universidade Federal do Paraná, pela seguinte banda examinadora:

Orientador: Prof. José Manoel Fernandes, Ph.D.

Departamento de Engenharia Elétrica, UFPR.

Prof. Leandro dos Santos Coelho, Dr.

Departamento de Engenharia Elétrica, UFPR.

Prof. Gideon Villar Leandro, Dr.

Departamento de Engenharia Elétrica, UFPR.

Prof. Eduardo de Freitas Rocha Loures, Dr.

Departamento de Engenharia Mecatrônica, PUC-PR.

Ao meu querido e amado filho, João Paulo, que todos os dias me motiva com seus convites irrecusáveis. - Papai, vamos brincar?

## **AGRADECIMENTOS**

Primeiramente agradeço a Deus, pois sem Ele nada é possível.

Ao amigo e Prof. José Manoel Fernandes, Ph.D. por todo apoio, conselhos, orientações e por acreditar neste trabalho.

Aos professores do programa de Pós-Graduação em Engenharia Elétrica da UFPR pelo esforço constante em oferecer um ensino de qualidade e aos professores que aceitaram fazer parte desta banca.

Agradeço aos meus pais Luiz Soppa e Rejansira Soppa por todo amor, carinho, apoio incondicional e por sempre estarem ao meu lado.

A minha amada esposa Alexandra C. Guimarães, pela dedicação, apoio, carinho e pelas palavras de incentivo.

Ao meu filho João Paulo por me acordar com beijos nos sábados e nos domingos e a Maria Tereza pelos seus sorrisos, verdadeira fonte de alegria.

As minhas irmãs Luciane e Daniele por me apoiarem em vários momentos.

Ao amigo Eng. Juliano de Mello Pedroso, M.Sc. pelas sugestões e contribuições feitas a este trabalho. Que as experiências compartilhadas até aqui sejam a alavanca para alcançarmos à alegria de chegar ao destino por cada um de nós projetado.

Aos amigos do Senai, Marcio Debner, Carlos Sakiti e Marco Túlio pelos incontáveis debates na padaria na hora do intervalo, e a Miguel Igino por confiar em meu trabalho.

A todos aqueles que diretamente ou indiretamente contribuíram para a realização desta dissertação. E, a todos aqueles que entenderam a minha ausência durante este período.

Ao Senai-CIC pela infra-estrutura cedida para a realização deste estudo.

Se sou fiel no pouco, Ele me confiará mais. Se sou fiel no pouco, meus passos guiará.

#### **RESUMO**

Os Sistemas Instrumentados de Segurança (SISs) são sistemas responsáveis pela segurança operacional de unidades e equipamentos industriais. Eles causam a parada de emergência (ESD - Emergency Shutdown) ou impedem uma operação insegura sempre que as condições do processo ultrapassem os limites préestabelecidos como seguros. Após alguns acidentes fatais, com perda de vidas humanas, agressão do meio ambiente, começou-se a por em prática o conhecimento em segurança e o desenvolvimento de sistemas. Isso refletiu em normas nacionais (N-2595) e internacionais (IEC-61508, IEC-61511, TR-84.01) no desenvolvimento de produtos específicos para serem usados na concepção e arquitetura de novos projetos de instalações. Existem diferentes tipos de sistemas (arquitetura) que atendem a diferentes processos. Muitas vezes, após ter sido feita a qualificação da malha de controle, o preço é quem decide qual sistema será implantado, transformando o custo do sistema em um item de decisão, desde que os sistemas analisados atendam o mesmo nível de integridade de segurança (SIL -Safety Integrity Level). O objetivo desta dissertação é propor e validar de forma prática um Sistema Redundante de Segurança utilizando o hardware de um PC (Personal Computer) padrão, uma vez que este hardware já está bem testado. Ainda, demonstrar que é possível o desenvolvimento de SIS de baixo custo, tão eficiente quanto os sistemas existentes no mercado. A diferença entre o sistema proposto e um computador de uso comum será o sistema operacional, pois neste projeto irá ser utilizado um sistema embarcado (Windows CE) no lugar dos sistemas operacionais conhecidos, de maneira que os erros provenientes do software que ocorrem nos computadores sejam eliminados. Para que se tenha a redundância modular tripla (TMR – *Triple Modular Redundant*) irá ser colocado três computadores com sistema embarcado para processar as informações em paralelo (ao mesmo tempo). Para que a interface com o mundo externo (sensores, transmissores e atuadores) seja feita, placas de comunicação se farão necessárias, conversores de corrente para tensão, conversor de pulso PWM (Pulse Width Modulation) para sinal analógico e modulação em corrente etc. Todo o sistema será testado em uma planta didática e deverá efetuar o controle de vazão de uma malha, utilizando para tanto um algoritmo PID (Proporcional Integral e Derivativo) devidamente sintonizado. Ainda, será identificada a probabilidade de falha sobre demanda (PFD) para que seja possível a qualificação do sistema de acordo com a norma IEC 61508.

**Palavras–chave**: Sistema Instrumentado de Segurança (SIS). Nível de Integridade de Segurança (SIL – *Safety Integrity Level*). Sistema embarcado. Controle. PID (Proporcional Integral e Derivativo). Probabilidade de Falha sobre Demanda (PFD). IEC 61508. Redundância Modular Tripla (TMR - *Triple Modular Redundant*). Paralelo. Intertravamento. Windows CE.

#### **ABSTRACT**

The Safety Instrumented Systems (SISs) are systems responsible for the industrial units and equipments operational safety. They cause emergency stops (ESD – Emergency Shutdown) or prevent unsafe actions whenever the process conditions go outside pre-established safety limits. After several fatal accidents, like loss of human lives and environmental harm that the safety knowledge and systems design was put in practice resulting in national (N-2595) and international (IEC-61508, IEC-61511, TR-84.01) norms to be used in specific products for concept and design of new installation projects. Many times after loop qualification its price influences which system will be implemented, making the system's cost in a decision item, since all analyzed systems meet the same Safety Integrity Level (SIL). The objective of this dissertation is to propose and validate in a practical way a redundant safety system using a standard PC (Personal Computer) hardware. As this hardware is widely tested and proven to work, it can be demonstrated that a low cost SIS can be developed as effective as other existing market SIS. A difference between the proposed system and one common use computer will be the operating system, because an embedded system (Windows CE) instead of known operating systems. can debug known errors. To obtain a Triple Modular Redundancy (TMR) three computers with embedded system will process the information in parallel (at the same time). For external interface (sensors, transmitters and actuators) communication boards will be developed, current to voltage converters, pulse PWM (Pulse Width Modulation) for analogical signals, current modulation among others. All this system will be employed in a didactic plant and must execute flow control in a loop using a PID (Proportional Integral Derivative) algorithm. And the, failure probability over demand (PFD) will still be identified, so it will be possible to qualify the system in accordance with the norm IEC61508.

**Keywords**: Sistema Instrumentado de Segurança (SIS). *Safety Integrity Level* (SIL). Embedded System. Control. Proportional Integral Derivative (PID). Failure Probability over Demand (PFD). IEC 61508. Triple Modular Redundancy (TMR). Parallel. Interlock. Windows CE.

# LISTA DE ILUSTRAÇÕES

| FIGURA 1 – ETAPAS METODOLÓGICAS                               | 19  |

|---------------------------------------------------------------|-----|

| FIGURA 2 – ALARP                                              | 26  |

| FIGURA 3 – CAUSA COMUM                                        | 39  |

| FIGURA 4 – SISTEMA DE REDUNDÂNCIA MODULAR TRIPLA              | 42  |

| FIGURA 5 – SISTEMA HOT STANDBY                                | 43  |

| FIGURA 6 – BLOCOS DE RECUPERAÇÃO.                             | 44  |

| FIGURA 7 – O IMPACTO DA REDUNDÂNCIA                           | 45  |

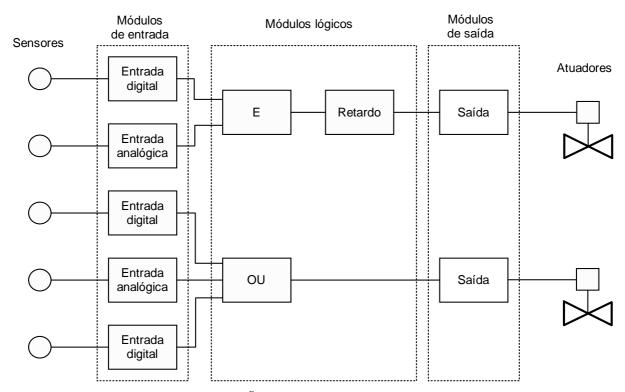

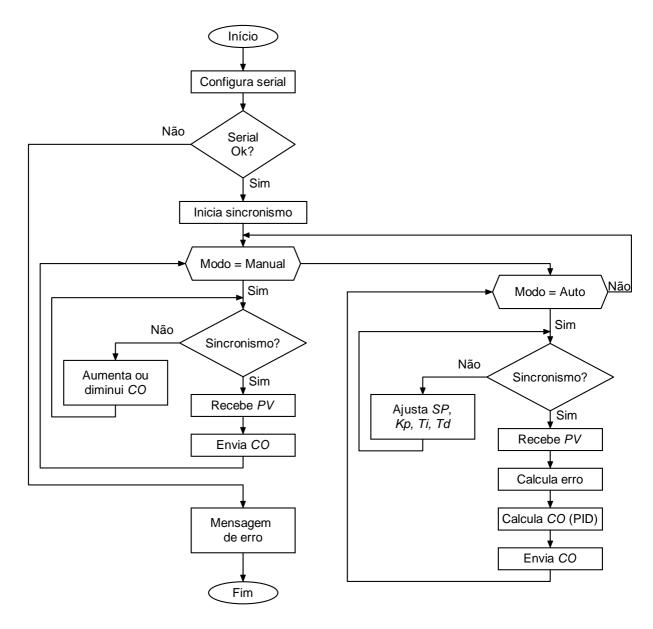

| FIGURA 8 – SISTEMA DE CONTROLE                                | 52  |

| FIGURA 9 – SISTEMA A MALHA ABERTA.                            | 52  |

| FIGURA 10 – SISTEMA A MALHA FECHADA                           | 53  |

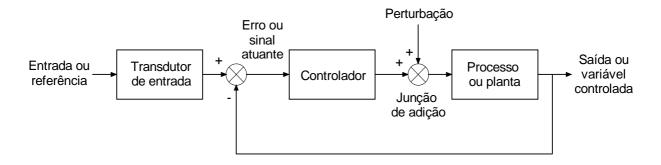

| FIGURA 11 – SISTEMA DE CONTROLE CLÁSSICO.                     | 55  |

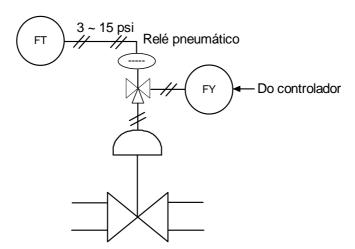

| FIGURA 12 – SISTEMA DE PARADA PNEUMÁTICO                      | 58  |

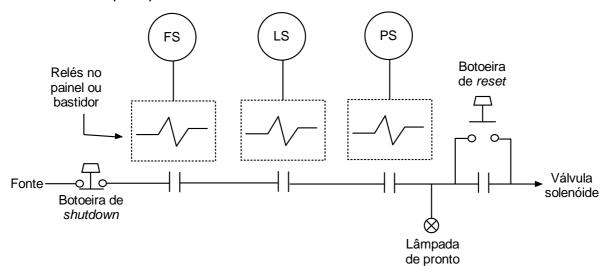

| FIGURA 13 – SISTEMA A RELE TÍPICO                             | 60  |

| FIGURA 14 – CONCEITO DE OPERAÇÃO                              | 61  |

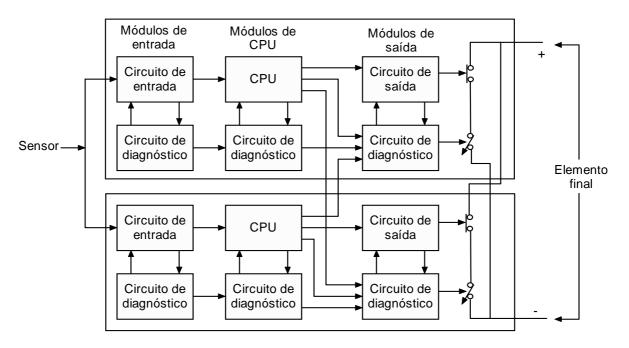

| FIGURA 15 – SISTEMA 2002 COM DIAGNÓSTICO                      | 64  |

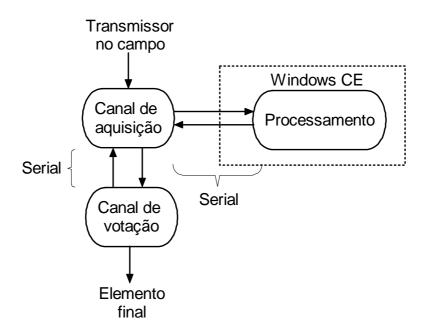

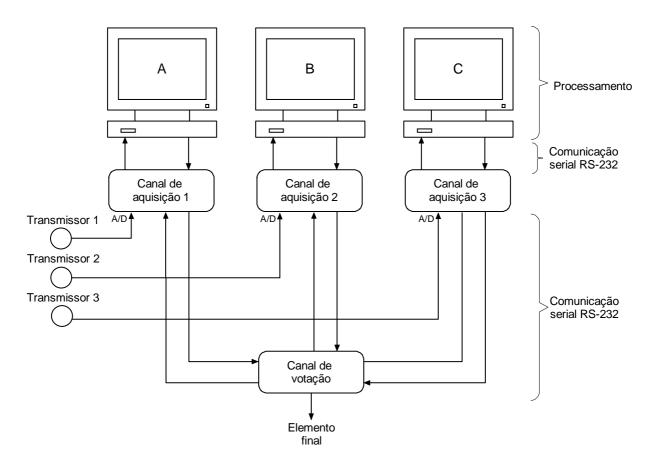

| FIGURA 16 – DIAGRAMA DE BLOCOS DE UM CANAL DO SISTEMA PROPOST | ГΟ. |

|                                                               | 65  |

| FIGURA 17 – DIAGRAMA DE INTERLIGAÇAO                          | 66  |

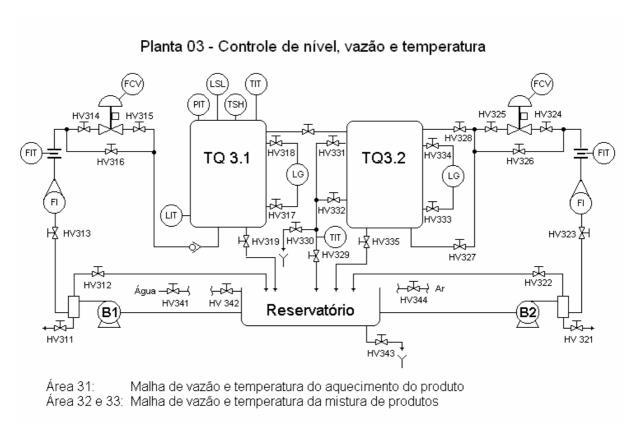

| FIGURA 18 – DIAGRAMA DA PLANTA 3                              | 68  |

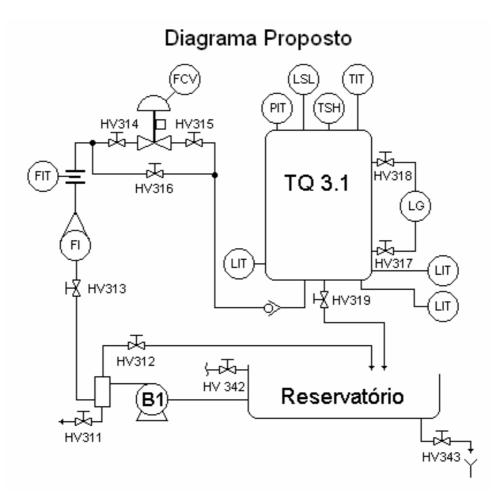

| FIGURA 19 – DIAGRAMA PROPOSTO                                 | 70  |

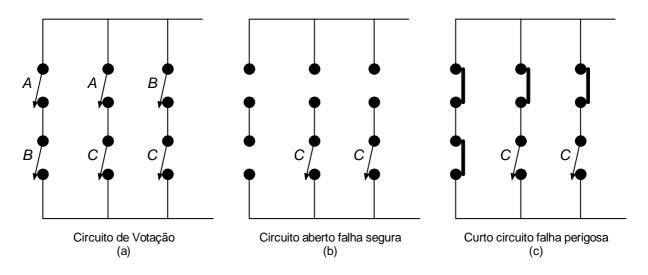

| FIGURA 20 – MODOS DE FALHA DA ARQUITETURA 2003                | 72  |

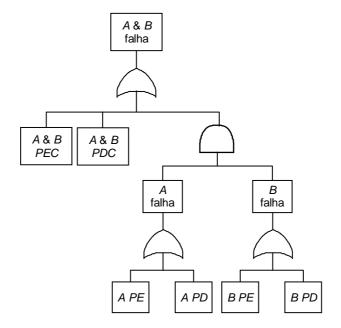

| FIGURA 21 – ÁRVORE DE FALHA DE UMA ARQUITETURA 2003 PARA OS   |     |

| CANAIS A e B.                                                 | 72  |

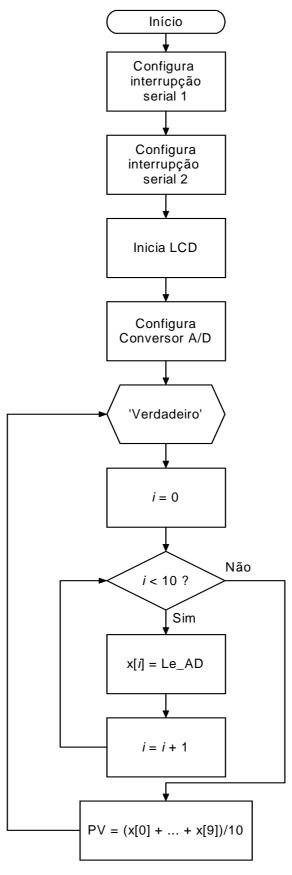

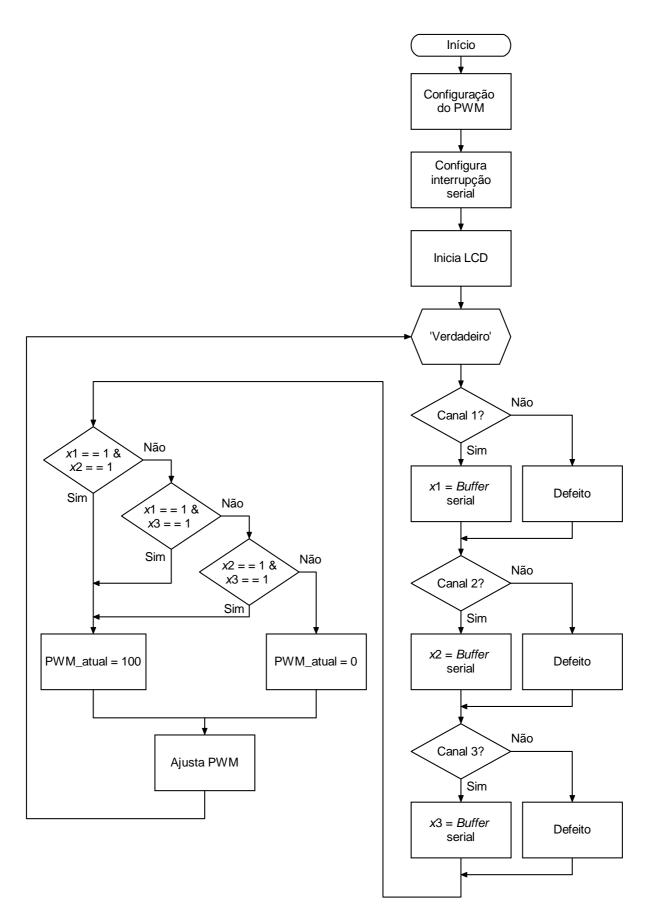

| FIGURA 22 – FLUXOGRAMA DO ALGORITMO DO CANAL DE AQUISIÇÃO     | 75  |

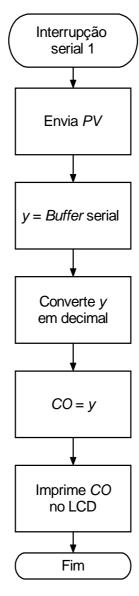

| FIGURA 23 – FLUXOGRAMA DA FUNÇÃO DE TRATAMENTO DA INTERRUPÇ   | ÃO  |

| SERIAL 1                                                      | 76  |

| FIGURA 24 - FLUXOGRAMA DA FUNÇÃO DE TRATAMENTO DA INTERRUPÇÃ  | ÃΟ  |

| SERIAL 2                                                      | 77  |

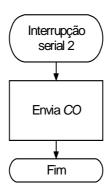

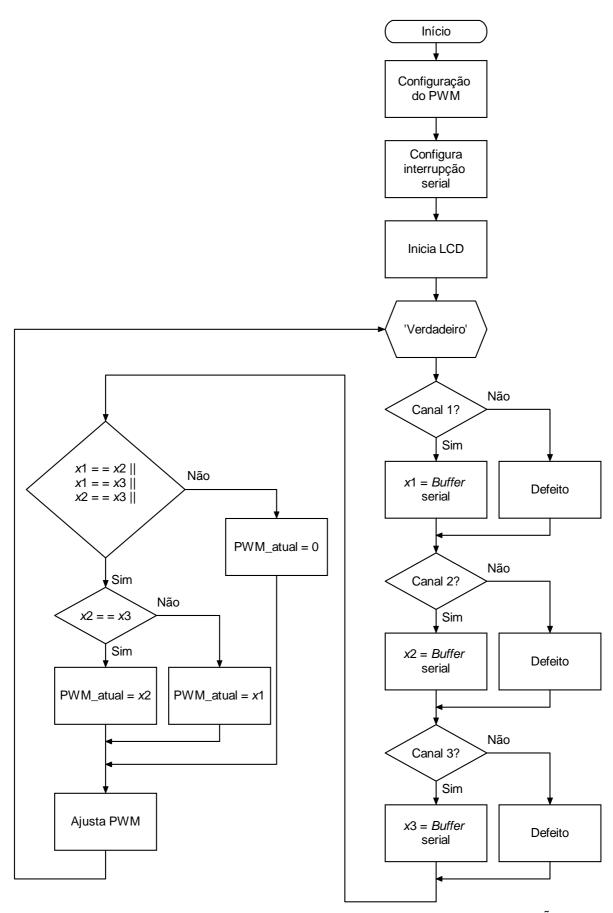

| FIGURA 25 – FLUXOGRAMA DO ALGORITMO DE CONTROLE DO CANAL DE   |     |

| VOTAÇÃO                                                       | 79  |

| FIGURA 26 – FLUXOGRAMA DO ALGORITMO DE <i>SHUTDOWN</i> DO CANAL DE |    |

|--------------------------------------------------------------------|----|

| VOTAÇÃO                                                            | 80 |

| FIGURA 27 – FLUXOGRAMA DA TROCA DE DADOS ENTRE O CANAL DE          |    |

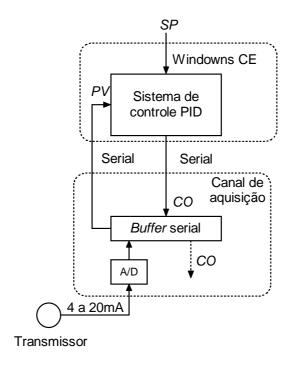

| AQUISIÇÃO E O WINDOWS CE                                           | 85 |

| FIGURA 28 – FLUXOGRAMA DO SISTEMA DE CONTROLE                      | 86 |

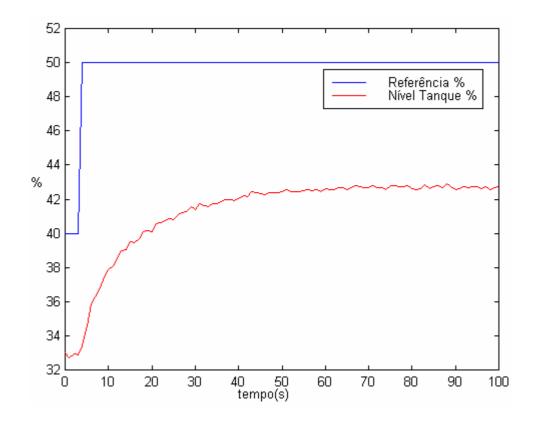

| FIGURA 29 – CURVA DE RESPOSTA DO SISTEMA EM MALHA ABERTA           | 87 |

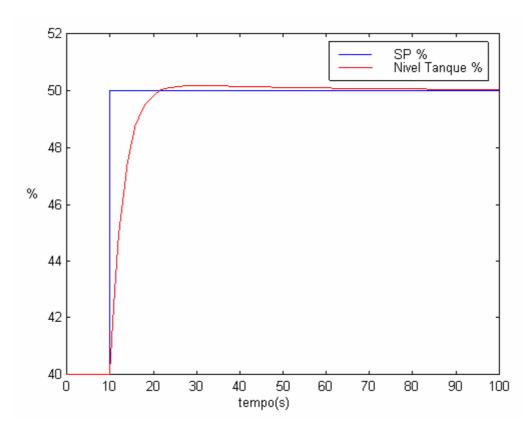

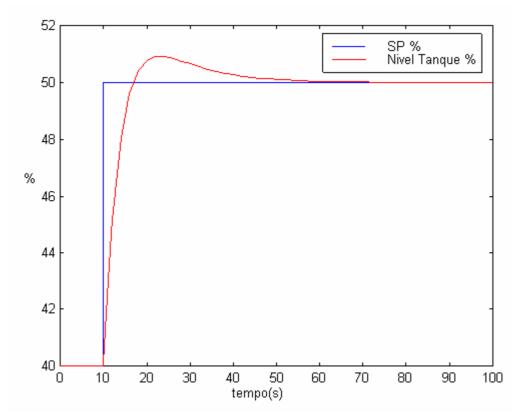

| FIGURA 30 – CURVA DE RESPOSTA DO PROCESSO CONTROLADO PELO          |    |

| SISTEMA                                                            | 89 |

| FIGURA 31 – CURVA DE RESPOSTA DO PROCESSO CONTROLADO POR UM        | M  |

| CONTROLADOR INDUSTRIAL                                             | 89 |

| FIGURA 32 – DIAGRAMA ESQUEMÁTICO DO SISTEMA 2003                   | 91 |

| FIGURA 33 – FLUXOGRAMA DO SISTEMA DE INTERTRAVAMENTO               | 93 |

## **LISTA DE TABELAS**

| TABELA 1 – NÍVEL DE INTEGRIDADE DE SEGURANÇA IEC 61508 VERSUS       |    |

|---------------------------------------------------------------------|----|

| DIN/VDE 19250                                                       | 23 |

| TABELA 2 - SIL EM FUNÇÃO DE DISPONIBILIDADE E PROBABILIDADE DE      |    |

| FALHA SOB DEMANDA                                                   | 33 |

| TABELA 3 – CÁLCULO DE $PFD$ E $MTTF_{sp}$ PARA SISTEMAS REDUNDANTES | 35 |

| TABELA 4 – TABELA DE CLPs DE SEGURANÇA CERTIFICADOS IEC 61508       | 63 |

| TABELA 5 – EQUIPAMENTOS E SUAS FUNÇÕES                              | 68 |

| TABELA 6 – CONJUNTO DE CARACTERÍSTICAS UTILIZADAS PARA A            |    |

| CONSTRUÇÃO DA IMAGEM NO WINDOWS CE                                  | 82 |

| TABELA 7 – TABELA VERDADE DE SAÍDA DE CADA CANAL DE                 |    |

| PROCESSAMENTO DADA AS ENTRADAS (SA,SB e SC)                         | 91 |

| TABELA 8 – FALHAS SEGURAS                                           | 94 |

| TABELA 9 – FALHAS PERIGOSAS                                         | 95 |

## LISTA DE SIGLAS

AIChE - Instituto Americano de Engenheiros Químicos

ALARP - As Low as Reasonably Possible

ANSI - American National Standards Institute

API - American Petroleo Institute

CCPS - Center for Chemical Process Safety

CE - Compact Edition

CLP - Controlador Lógico Programável

CO - Saída de Controle

CPU - Unidade Central de Processamento

DIN - Deutsches Institut fur Normung

EPA - Environment Program Agency

ESD - Emergency Shutdown

FMEA - Análise de Modos e Falhas e seus Efeitos

HAZOP - Hazard Operability

IEC - International Electrotechnical Commmission

ISA - Instrumentation and Automation Society

LED - Diodo Emissor de Luz LCD - Liquid Crystal Display

MMU - Memory Management Unit

MTBF - Tempo Médio entre Falhas

MTTF - Tempo Médio de Falha

MTTR - Tempo Médio de Reparo

MV - Variável Manipulada

NFPA - National Fire Protection Agency

NMR - Redundância Modular N

OMAC - Open, Modular, Architecture Control

OSHA - Occupational Safety and Heath Organization

PC - Personal Computer

PES - Sistema Eletrônico Programável

PFD - Probabilidade de Falha sobre Demanda

PHA - Process Harzard Analysis

PID - Proporcional, Integral e Derivativo

PSM - Risc Management Program

PV - Variável do Processo

PWM - Pulse Width Modulation

RRF - Fator de Redução de Risco

SAFE - Safety Function Evaluation

SDCD - Sistema Digital de Controle Distribuído

SIL - Nível de Integridade de Segurança

SIS - Sistema de Intertravamento de Segurança

SP - Set Point

TMR - Redundância Modular Tripla

TR - Technical Report

TUV - Technische Uberwachungs Verein

USB - Universal Serial Bus

WDT - Watchdog Timer

Win API - Application Programming Interface

# SUMÁRIO

| 1. INTRODUÇÃO                                                        | 15 |

|----------------------------------------------------------------------|----|

| 1.1. OBJETIVOS GERAIS                                                | 17 |

| 1.2. OBJETIVOS ESPECÍFICOS                                           | 17 |

| 1.3. ESTRUTURA DA DISSERTAÇÃO                                        | 18 |

| 1.4. ETAPAS METODOLÓGICAS                                            | 18 |

| 2. REVISÃO DA LITERATURA                                             | 20 |

| 2.1. OS SISTEMAS DE SEGURANÇA NOS PROCESSOS INDUSTRIAIS              | 20 |

| 2.2. NORMAS ATUAIS PARA SIS                                          | 21 |

| 2.3. ANÁLISE DO RISCO                                                | 23 |

| 2.3.1. Perigo ( <i>Hazard</i> )                                      | 23 |

| 2.3.2. Risco                                                         | 24 |

| 2.3.3. Conceitos de Risco                                            | 25 |

| 2.4. DEFINIÇÕES SOBRE SISTEMAS DE SEGURANÇA (SIS)                    | 27 |

| 2.4.1. Falhas                                                        | 29 |

| 2.4.2. Análise Quantitativa e Qualitativa                            | 31 |

| 2.4.3. Probabilidade de Falha sobre Demanda (PFD)                    | 32 |

| 2.4.4. Análise de Sistemas                                           | 35 |

| 2.4.4.1. Análise de um Sistema a Rele                                | 35 |

| 2.4.4.2. Análise de um Sistema com Controlador Lógico Programável ná | ĭo |

| redundante                                                           | 36 |

| 2.4.4.3. Análise de um Sistema de Redundância Tripla (TMR)           | 38 |

| 2.4.5. Causa Comum                                                   | 39 |

| 2.5. TIPOS DE REDUNDÂNCIA                                            | 40 |

| 2.5.1. Redundância de <i>Hardware</i>                                | 41 |

| 2.5.2. Redundância de Software                                       | 43 |

| 2.5.3. O Impacto da Redundância                                      | 45 |

| 2.6. SISTEMAS EMBARCADOS                                             | 46 |

| 2.6.1. Sistema de Tempo Real                                         | 47 |

| 2.6.2. Windows CE                                                    | 48 |

| 2.7. SISTEMA DE CONTROLE                                             | 51 |

| 2.7.1. Malha Aberta                                                  | 52 |

| 2.7.2. Malha Fechada                                        | 53  |

|-------------------------------------------------------------|-----|

| 2.7.3. Controlador PID                                      | 54  |

| 2.7.4. Controle em Tempo Real                               | 55  |

| 3. MATERIAIS E MÉTODOS                                      | 56  |

| 3.1. INTRODUÇÃO                                             | 56  |

| 3.2. ESCOLHA DA TECNOLOGIA E DA ARQUITETURA                 | 57  |

| 3.2.1. SIS Pneumáticos                                      | 58  |

| 3.2.2. SIS a Rele                                           | 59  |

| 3.2.3. SIS de Lógica Fixa em Estado Sólido                  | 60  |

| 3.2.4. SIS Microprocessado (CLP)                            | 62  |

| 3.3. PROPOSTA DE UM SISTEMA TOLERANTE A FALHAS              | 64  |

| 3.3.1. Planta Didática                                      | 67  |

| 3.3.2. Comparação do Sistema com CLP Industrial de Controle | 70  |

| 3.3.3. Obtenção de Dados para o Cálculo da PFD              | 71  |

| 3.4. AQUISIÇÃO DA PFD                                       |     |

| 4. IMPLEMENTAÇÃO E RESULTADOS                               | 74  |

| 4.1. CANAL DE AQUISIÇÃO                                     | 74  |

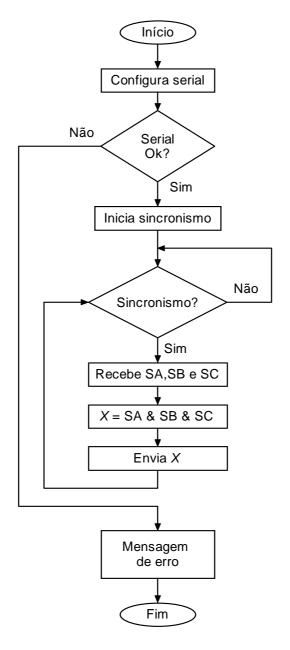

| 4.2. CANAL DE VOTAÇÃO                                       | 77  |

| 4.3. CANAL DE PROCESSAMENTO                                 | 81  |

| 4.3.1. Criando a Imagem do Windows CE                       | 81  |

| 4.3.2. Criando o Disco de BOOT                              | 83  |

| 4.3.3. Efetuando o BOOT Local                               | 83  |

| 4.3.4. Criando um Novo Projeto                              | 83  |

| 4.4. SISTEMA DE CONTROLE                                    | 84  |

| 4.5. SISTEMA DE INTERTRAVAMENTO                             | 90  |

| 5. CONCLUSÕES E TRABALHOS FUTUROS                           | 96  |

| REFERÊNCIAS                                                 | 99  |

| ANEXO A                                                     |     |

| APÊNDICE A                                                  |     |

| APÊNDICE B                                                  | 107 |

## **CAPÍTULO 1**

## 1. INTRODUÇÃO

O projeto de sistemas instrumentados de segurança ou sistemas de intertravamento de segurança (*shutdown*) era relativamente simples há trinta anos atrás (CCPS,1993), sem falar que não havia normas industriais sobre o assunto. De um modo geral a escolha recaía sobre reles. Mas a evolução não ocorre por acaso, nem apenas do desenvolvimento da consciência de que os acidentes podem e devem ser evitados. Infelizmente, é a partir de acidentes ocorridos nas indústrias de processos que se verificou que os sistemas de segurança normalmente empregados nas instalações industriais deixavam a desejar.

Após alguns acidentes fatais, como perdas de vidas humanas e agressão ao meio ambiente começaram-se a por em prática o conhecimento em segurança e o desenvolvimento de novos sistemas. Isso refletiu em normas nacionais e internacionais no desenvolvimento de produtos (*hardware* e *software*) específicos para serem usados na concepção e na arquitetura de novos projetos de instalações.

Os trabalhos nesta área começaram há cerca de dez anos, tanto nos Estados Unidos como em outros países. O tema comum nas normas recentes é: "quanto maior o risco do processo, tanto melhor devem ser os sistemas necessários para controlar tal risco" (GRUHN;CHEDDIE, 2006).

Hoje em dia, existe uma gama grande de escolhas de possíveis tecnologias (por exemplo, tecnologias distintas, níveis de redundância, etc.), que as pessoas ficam confusas. É comum que inicialmente projetistas adotem uma postura muito conservadora, e demonstrem interesse em instalar os sistemas para atingir um desempenho SIL 3. Infelizmente, quando eles percebem que os sistemas que são certificados para atender este nível são caros, eles acabam precisando encontrar uma outra saída, por exemplo, reavaliar a malha de controle para tentar baixar o SIL (Nível de Integridade de Segurança), o que gera um retrabalho e custos adicionais de projeto para as empresas.

Os sistemas SIL 1 proporcionam o menor nível de desempenho (de 90 a 99% de disponibilidade), basicamente para atender aos baixos níveis de risco de processos. Os sistemas SIL 3 oferecem os níveis de desempenho mais altos (de

99,9 a 99,99% de disponibilidade), para atender aos níveis mais elevados de risco do processo. As normas não obrigam e nem recomendam qual tecnologia deve ser usada, nem níveis de redundância ou intervalos de testes manuais devem ser adotados para atender os requisitos de desempenho para níveis de integridade distintos. Cabe ao projetista determinar quais sistemas foram projetados para atender às condições de segurança. Alguns livros de confiabilidade como Xai, Dai e Poh (2004) e Pham (2003), bem como, o relatório TR 84.01 da ISA e a norma IEC 61508 mostram métodos para o cálculo do desempenho de segurança de um sistema.

Os sistemas a reles têm condições de atender aos requisitos SIL 3, mas é raro encontrar, hoje em dia, alguém disposto a usar reles para grande sistemas. Os sistemas baseados em *software* e *hardware* com redundância dupla e tripla também são capazes de atender aos requisitos SIL 3. Esses sistemas também são certificados por órgãos independentes como TUV e Exida.

A sugestão deste trabalho é partir de um *hardware* e de um *software* existente e exaustivamente testado pelas diversas aplicações que o envolvem. A evolução dos PCs acarreta uma alta confiabilidade de *hardware* e o surgimento dos sistemas embarcado de tempo real vem aumentando as possibilidades de se ter novos sistemas desenvolvidos a partir da arquitetura do PC que apresentem uma alta disponibilidade e confiabilidade.

A questão é que, dentro de sistemas dedicados para SIL o processamento é feito com microcontroladores ou microprocessadores que estão disponíveis no mercado. Em sistemas mais antigos, pode-se encontrar microprocessadores inferiores aos existentes e utilizados hoje em dia nos PCs. Então, a indústria de sistema é obrigada a desenvolver todo um *hardware* específico e dedicado que tem um alto custo de desenvolvimento para atingir a disponibilidade exigida. E dentro destes *hardwares* existem *softwares* embarcados denominados *firmwares* que servem para rodar o programa aplicativo desenvolvido pelo usuário.

O objetivo é utilizar a arquitetura de um PC, cuja diferença reside no sistema operacional. Para tanto, utilizar-se-á um sistema operacional de tempo real, que pode ser comparado com o *firmware* dos sistemas dedicados. Será criado um aplicativo que irá rodar em cima deste *firmware*, podendo este aplicativo ser comparado com o *software* desenvolvido pelo usuário.

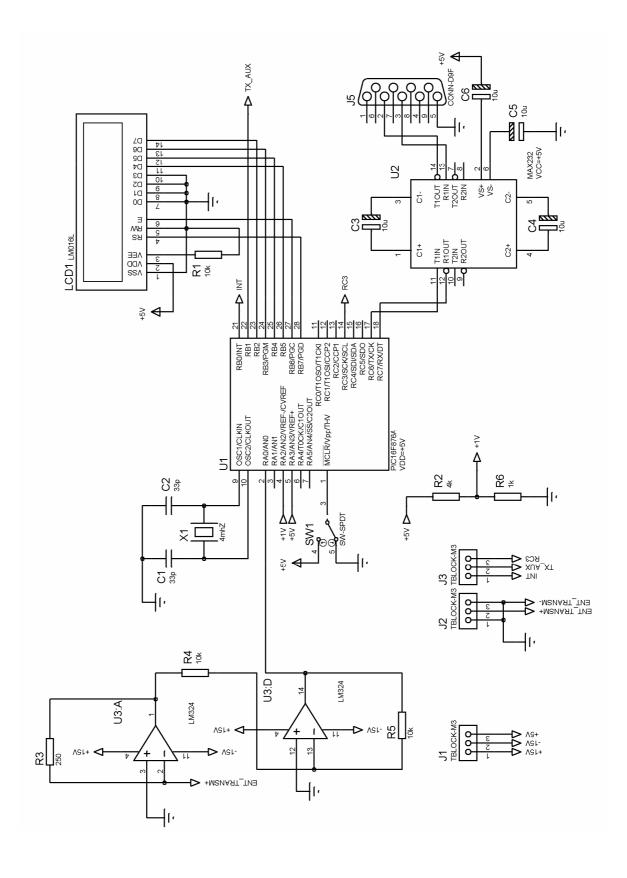

Para que seja possível a interface do aplicativo desenvolvido com os equipamentos de campo (sensores, elementos finais, etc.) serão desenvolvidas placas que se comunicarão com o PC via um protocolo serial.

Feito isto, as normas de certificação de sistemas de intertravamento de segurança serão seguidas para que seja possível o cálculo de disponibilidade do sistema proposto, visando à avaliação de todo este trabalho e validação do mesmo.

## 1.1. OBJETIVOS GERAIS

Estudar os diferentes sistemas de redundância existentes no mercado (sistemas pneumáticos, a reles, lógica fixa e controladores lógicos programáveis), verificar seus funcionamentos e benefícios, analisar as vantagens e desvantagens de tais sistemas, com isto, propor um sistema concorrente de baixo custo, mas tão eficaz quanto. Para tanto, implementar um sistema utilizando-se de um *hardware* padrão (PC) e um sistema e*mbedded* sem precisar desenvolver um sofisticado novo *hardware*.

## 1.2. OBJETIVOS ESPECÍFICOS

Os objetivos específicos são:

- Checar os vários sistemas disponíveis no mercado;

- Propor um sistema de baixo custo com confiabilidade;

- Comparar o sistema proposto com sistemas industriais;

- Aplicar o sistema proposto em um processo real;

- Calcular a disponibilidade do sistema proposto;

- Encontrar o SIL deste sistema de acordo com a IEC 61508.

- Verificar se o sistema proposto atende as exigências industriais, seguindo a prescrição da IEC 61508.

## 1.3. ESTRUTURA DA DISSERTAÇÃO

O restante desta dissertação está organizada em 4 capítulos. No Capítulo 2 faz-se uma revisão da literatura sobre os principais conceitos sobre nível de integridade de sistemas, sistema operacional de tempo real. No Capítulo 3, descrevem-se em detalhes o desenvolvimento do sistema redundante proposto. No Capítulo 4 relatam-se os resultados obtidos. E, finalmente, o Capítulo 5 apresenta a discussão dos resultados, as conclusões do trabalho e as propostas de trabalhos futuros.

## 1.4. ETAPAS METODOLÓGICAS

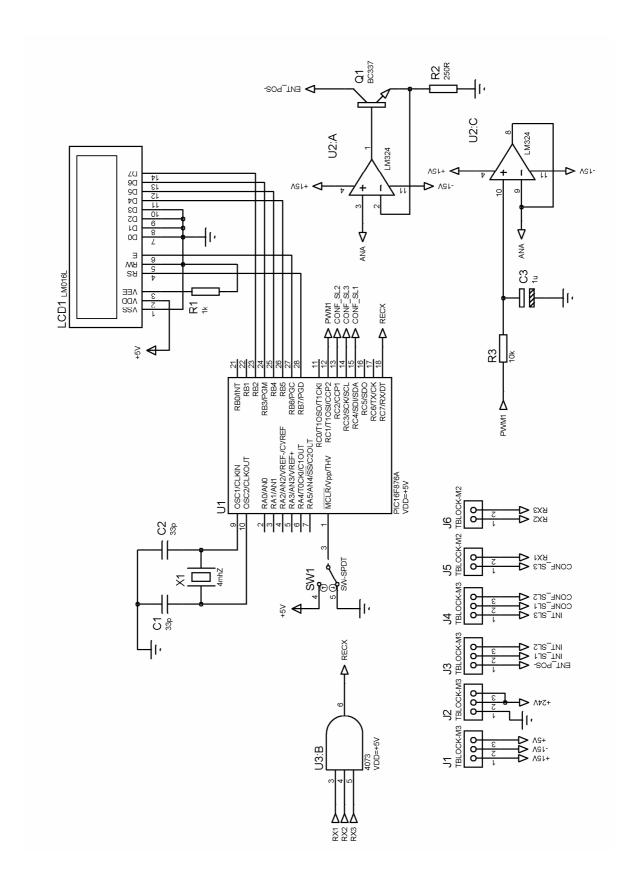

A metodologia desta pesquisa esta apoiada na elaboração de um protótipo fundamentado pela IEC 61508 que é a norma que certifica este tipo de equipamento. A validação do mesmo foi baseada na norma em questão, para tanto, dois experimentos serão desenvolvidos, o primeiro focando uma aplicação em controle de processo e o segundo para um sistema de intertravamento. A Figura 1 ilustra essas etapas metodológicas.

As etapas metodológicas da pesquisa tem por objetivo as seguintes atividades e resultados:

- 1. Normas, SIL e redundância: revisão bibliográfica para encontrar a forma que é aplicada a IEC 61508 para encontrar o SIL de uma malha de controle.

- 2. Pneumático, Rele, Lógica fixa, CLP redundante: Analisar as tecnologias existentes no mercado afim de elencar as suas vantagens e desvantagens.

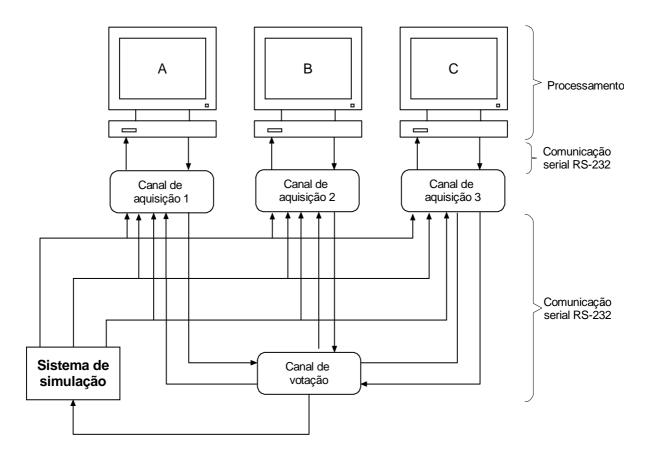

- 3. Canais de aquisição, votação e processamento: propor um sistema redundante a falhas com uma configuração 2003.

- Validação em uma malha de controle: aplicação em um processo real a fim de comparar o sistema proposto com um sistema industrial.

Validação em um sistema de intertravamento: obter as taxas de falhas do sistema proposto para encontrar a disponibilidade, confiabilidade e o SIL deste sistema de acordo com a IEC 61508.

FIGURA 1 - ETAPAS METODOLÓGICAS.

## **CAPÍTULO 2**

## 2. REVISÃO DA LITERATURA

## 2.1. OS SISTEMAS DE SEGURANÇA NOS PROCESSOS INDUSTRIAIS

Os sistemas de *shutdown* (ESD, SIS) para processos industriais têm evoluído bastante nestas últimas décadas, em termos de concepção, projeto e implementação. A evolução não é fruto do acaso, nem apenas do desenvolvimento de uma consciência de que os acidentes podem e devem ser evitados. Infelizmente, é a partir da análise de acidentes realmente ocorridos que se tomou conhecimento de que os sistemas de segurança normalmente empregados em instalações industriais deixavam a desejar (FINKEL *et al.*, 2006).

Um fator importante, para a ocorrência do acidente, é o excesso de autoconfiança, não só entre operadores, mas principalmente, em níveis gerenciais. Para não parar o processo, frequentemente assumem-se riscos desnecessários, e frequentemente o resultado é o acidente. Antes do ocorrido em Chernobil, um primeiro ministro soviético disse textualmente: "Nossos reatores nucleares são tão seguros que poderia-se instalar um aqui na Praça Vermelha, no centro de Moscou" (FINKEL *et al.*, 2006).

Após o acidente na plataforma de Piper Alfa ficou provado que não se pode confiar na capacidade de decisão/atuação do ser humano frente ao *stress* de um acidente grave. Posteriormente, estudos revelaram que, estatisticamente, quando submetidos à forte fator de *stress*, seres humanos tomam iniciativas erradas em 99% dos casos. Conclusão: o sistema de desligamento de emergência não pode depender de acionamento manual, devem ser acionados automaticamente (FINKEL *et al.*, 2006).

O excesso de confiança também atinge os sistemas de segurança, que muitas vezes não são exaustivamente testados com a frequência necessária para garantir uma probabilidade de falha suficientemente pequena. O problema surge na hora de testar os elementos finais. A única maneira de saber se uma válvula de

shutdown realmente está em boas condições de atuação, e que provavelmente vai fechar mesmo em caso de necessidade, é comandar a válvula para fechar e aguardar o seu fechamento completo. Mas infelizmente. isso é caro porque provoca a parada do processo (GRUHN; CHEDDIE, 2006).

#### 2.2. NORMAS ATUAIS PARA SIS

Segundo Gruhn e Cheddie (2006), as normas desempenham vários papéis na execução de um projeto, principalmente em SIS. Como exemplo, pode-se citar o auxílio à equipe de projeto, no sentido de garantir que o produto em desenvolvimento obedeça a um determinado nível mínimo de qualidade e a função de seleção de métodos de projeto de eficiência reconhecida.

Outras funções que podem ser citadas são promover uniformidade entre diversas equipes de trabalho, prover guias de projeto, além de proporcionar uma base legal no caso de disputas judiciais.

Para se certificar um sistema, normalmente, faz-se necessária a utilização de normas apropriadas a cada aplicação. Algumas normas são genéricas e outras se aplicam a casos particulares. Nos próximos itens são descritos os principais objetivos de algumas das normas mais utilizadas no desenvolvimento de Sistemas de Segurança Instrumentado.

De acordo com Finkel et al. (2006), as normas sobre Sistemas Instrumentados de Segurança (SIS) têm como denominador comum não serem normas prescritivas e sim orientadas para exigir que se atinja um nível de desempenho desejado pelo sistema. Elas dizem o que precisa ser feito, mas não como fazê-lo. Exige do profissional que as usa um conhecimento de causa bem maior do que quem queira simplesmente seguir uma receita de "como se projeta" um sistema. A norma pode ser aplicada com qualquer tipo de tecnologia existente ou futura. Assim a tendência é não ser necessária se revisar a norma a cada vez que surgir uma nova tecnologia aplicável a sistemas de segurança, o que seria indesejável, levando-se em conta o tempo de estudo, maturação e aprovação destas normas.

A exceção é a norma N-2595 (Critérios de projeto e manutenção para sistemas instrumentados de segurança em unidades industriais) onde se tenta manter uma prescrição de como projetar um Sistema de Segurança, inclusive sugerindo a tecnologia a ser escolhida em função da classificação do risco envolvido em cada malha. Assim: para malhas classe I ou II pode-se implementar o *shutdown* no SDCD (Sistema Digital de Controle Distribuído), enquanto para malhas classe III e superiores, é preciso implementar a segurança em equipamentos independentes do SDCD.

Para malhas classe III, o sistema pode ser implementado em reles (só para sistemas simples ou pequenos) ou em CLP (Controlador Lógico Programável) de segurança desde que aprovado para esta classe pelo TUV (*Technische Uberwachungs Verein -* ANEXO A) Organizações de Inspeção Técnica, conforme Anexo A.

Para malhas de classe superior a III, o sistema deve ser desenvolvido em CLP de segurança, aprovado para a classe da malha considerada, pelo TUV.

A Functional Safety - Safety Related Systems - Norma IEC 61508, da Comissão Eletrotécnica Internacional (Européia), de 1996, abrange todos os tipos de indústrias, incluindo medicina, transporte, nuclear, etc., e cobrindo várias tecnologias como reles, lógica fixa em estado sólido e sistemas programáveis. A norma IEC 61511 é derivada desta, porém destinada para as indústrias de processamento em geral.

Application of Safety Instrumented Systems for the Process Industries - ISA TR 84.01, da ISA (*The International Society for Measurement and Control*), de 1996. Norma aprovada pela ANSI, levou 11 anos em elaboração, inicialmente pretendia cobrir apenas a parte lógica do sistema em lógica programável, mas acabou abrangendo também os dispositivos de campo e outras tecnologias. É considerada pelos Americanos como uma Norma Internacional. Pode vir a conflitar (ou se tornar obsoleta ou ser substituída) pela IEC- 61511.

A Diretriz PES Guidelines (Programmable Electronic Systems for Use in Safety Related Applications) da Secretaria de Saúde e Segurança do Reino Unido, de 1997. Foi uma das primeiras normas publicadas a respeito do uso de PLCs em segurança, e embora focada em Sistemas Programáveis, é aplicável a outras tecnologias. Foi ponto de partida para a elaboração de outras normas européias e americanas.

Guidelines for Safe Automation of Chemical Processes, do Centro para Segurança do Processo (CCPS) do Instituto Americano de Engenheiros Químicos (AIChE) de 1993. Discorre sobre o uso de SDCDs (Sistema Digital de Controle Distribuído) e sistemas de intertravamento. Gerado por usuários, sem a interferência de fornecedores, o que permitiu uma velocidade de trabalho superior à usual neste tipo de comitê.

DIN/VDE 0801 é uma norma Alemã, apenas para os fabricantes dos sistemas. Detalha exigências para fabricação baseados nos riscos calculados conforme a norma DIN/VDE 19250, que por sua vez deve ser substituída pela IEC 61508. Os alemães têm uma agência de certificação independente, que é praticamente a única reconhecida mundialmente, para sistemas de segurança, a TUV.

Uma diferença significativa entre a IEC 61508 e a DIN/VDE 19250 é a classificação dos níveis de integridade de segurança, que pode ser observada na Tabela 1.

TABELA 1 – NÍVEL DE INTEGRIDADE DE SEGURANCA IEC 61508 VERSUS DIN/VDE 19250

| IEC 61508    | Arquitetura               | DIN/VDE 19250 |

|--------------|---------------------------|---------------|

| SIL 4        | Lógica fixa, falha segura | AK 8          |

|              |                           | AK 7          |

| SIL 3        | 1002D, 2003               | AK 6          |

|              |                           | AK 5          |

| SIL 2        | 1001D                     | AK 4          |

| SIL 1        | 1oo1 com WDT              | AK 3          |

|              |                           | AK 2          |

| Não definido | Não definido              | AK 1          |

## 2.3. ANÁLISE DO RISCO

## 2.3.1. Perigo (Hazard)

O Instituto Americano de Engenheiros Químicos (AIChE) define perigo como uma característica inerente físico ou químico que tem o potencial para causar danos às pessoas, bens ou o ambiente. Ele é a combinação de um material perigoso, um

ambiente operacional, e certos acontecimentos não planejados que podem resultar em um acidente.

Os perigos estão sempre presentes. Por exemplo, a gasolina é um combustível líquido. Enquanto não existe uma fonte de ignição, a gasolina pode ser considerada relativamente benigna. Nosso objetivo é minimizar ou eliminar eventos ou acidentes perigosos. Por isso, não devemos armazenar gasolina perto de fontes de ignição (GRUHN;CHEDDIE, 2006).

A N-2595 diz que perigo é uma causa potencial de dano à integridade física e saúde, patrimônio, meio ambiente ou perda de produção (PETROBRAS, 2002).

## 2.3.2. Risco

De acordo com a N-2595 risco é a combinação da taxa de perigo com as consequências do evento perigoso (PETROBRAS, 2002).

O risco normalmente é definido como a combinação da gravidade e da probabilidade de um evento perigoso. O risco pode ser avaliado qualitativamente ou quantitativamente (GRUHN;CHEDDIE, 2006).

Segundo Finkel *et al.* (2006) o risco é uma combinação de dois fatores:

- a probabilidade da ocorrência do evento indesejável;

- a consequência da ocorrência.

Assim, um evento desfavorável que ocorra com frequência, porém de consequências mínimas, pode corresponder ao mesmo nível de risco que um evento raríssimo, porém, de consequências catastróficas.

A aceitabilidade de um determinado nível de risco é determinada pelos benefícios associados à aplicação crítica e, consequentemente, seus riscos, bem como pelos esforços necessários para que se consiga a redução desses riscos. Riscos com consequências catastróficas e que ocorram frequentemente não são toleráveis em nenhuma hipótese. Por outro lado, riscos com consequências não significativas, mesmo com ocorrência frequente, podem ser aceitáveis.

A norma IEC 61508 classifica o risco em três níveis (Comissão Eletrotécnica Internacional (IEC), 1997):

- Risco Intolerável: as consequências do risco são intoleráveis e sua ocorrência não pode ser justificada;

- Risco Inaceitável: as consequências do risco são inaceitáveis, embora possam ser suportadas sob certas condições;

- Risco Negligenciável: as consequências do risco são insignificantes e podem ser desprezadas.

## 2.3.3. Conceitos de Risco

Tanto para Finkel *et al.* (2006) como para Gruhn e Cheddie (2006), um conceito bem difundido em Sistemas Instrumentados de Segurança, mas errôneo, diz que todos os processos vão para o estado seguro quando os equipamentos são desligados. Vamos analisar um exemplo, uma caldeira quando desligada deve ser ventilada internamente para a diluição de gases combustíveis até se atingir um nível de segurança, antes que se possa partir novamente, ou que a eventual concentração de gases quentes junto a algum ponto mais quente dentro da caldeira possa levar a uma ignição espontânea destes gases. É comum que ventiladores de tiragem tenham uma alimentação de emergência para poderem ser acionadas, mesmo que uma caldeira pare por perder sua alimentação elétrica normal.

Planta desligada não significa planta segura. O conceito que todo processo reverte a uma condição segura quando se corta a alimentação elétrica geral da planta, pode ser falso em muitas instalações.

Uma unidade industrial que entra em parada de emergência por uma falha no sistema de parada de emergência, na verdade, pode estar em uma condição bem menos segura do que o desejado. É mais seguro garantir que o SIS não provocará muitas atuações desnecessárias.

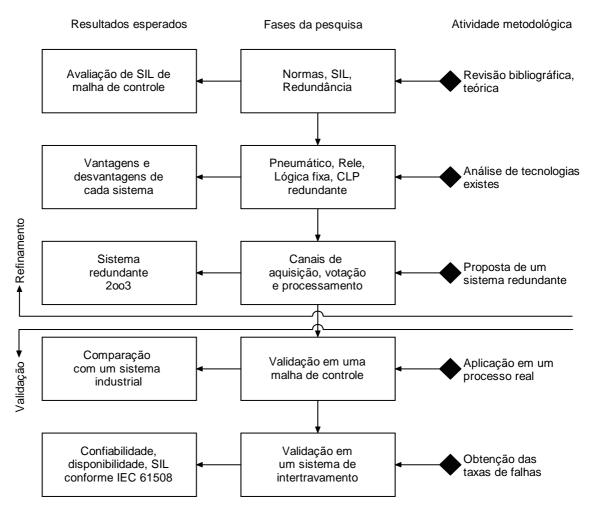

No caso de SIS, um determinado risco é aceitável se atingir um nível baixo o suficiente, de forma que reduções maiores não sejam justificáveis dos pontos de vista técnico e econômico. Esse é o princípio ALARP (As Low as Reasonably

Possible), ou seja, o risco deve ser tão baixo quanto o razoavelmente praticável ou implementável (IEC, 1997). É importante considerar que um risco não é aceitável se ele puder ser facilmente reduzido. Portanto, mesmo um sistema com um nível de risco muito pequeno pode ser considerado como inaceitável se o seu nível de risco puder ser facilmente reduzido. Similarmente, um sistema que tenha um nível de risco significante pode satisfazer aos requisitos se ele oferecer benefícios suficientes e reduções do risco forem consideradas impraticáveis. A Figura 2 representa o princípio ALARP.

FIGURA 2 – ALARP. FONTE: INTECH BRASIL (2006).

O conceito do ALARP surgiu na Inglaterra, há algumas décadas, embora não tenha sido enunciado formalmente até a uns poucos anos. Entende-se que não há uma segurança total nem absoluta, o que se pretende fazer é sempre reduzir o nível de risco a um nível aceitável, e não a um hipotético risco igual a zero (FINKEL *et al.*, 2006).

Os riscos elevados não podem ser aceitos, há que reduzi-los, obviamente. Riscos muito pequenos podem até ser aceitos sem que se façam despesas adicionais para reduzi-los, pois não vale à pena realizar o investimento para reduzir riscos que em caso de acidentes, causem prejuízos pequenos. É mais barato correr o risco do que reduzí-lo. E riscos médios, nem tão pequenos que sejam desprezíveis, nem tão grandes que sejam absolutamente intoleráveis? Para estes a

técnica do ALARP recomenda simplesmente que se tome a decisão baseada no custo e benefício.

Pode-se exemplificar da seguinte forma, se por US\$ 3000 for possível reduzir um destes riscos a um nível aceitável, sempre valerá à pena fazer este investimento, mas se para esta função de segurança não muito crítica, for preciso gastar US\$ 1.000.000, talvez seja melhor economizar este dinheiro e simplesmente correr o risco, ou reduzi-lo a um nível ainda um pouco maior do que o que seria considerado bom. Imagine que ao classificar as funções de segurança quanto ao SIL, haja 20 funções em que se ficou em dúvida, SIL 0 ou SIL 1, enquanto outras 20 ficaram na balança entre SIL 1 e SIL2. Revisto o projeto acabaram todas 40 em SIL 1. SIL 1 nunca se refere a riscos de vida humana ou ferimentos sérios, etc., estes teriam sempre um SIL elevado. Se devido à condição particular daquela instalação cada malha SIL 1 custar, por exemplo, US\$ 50.000 devido a válvulas de grande diâmetro e material muito resistente à corrosão, etc (INTECH BRASIL, 2006).

Não faz sentido projetar o SIS para atender apenas às malhas que inicialmente se imaginava estarem entre SIL 1 e SIL 2, e economizar um milhão de dólares não instalando o SIS para as outras malhas? Obviamente, o risco de acidentes aumentou, mas não se está falando de acidentes fatais nem de ferimentos graves, perdas de equipamento caro de produção, etc., pois estes deveriam ter um SIL mais elevado (INTECH BRASIL, 2006).

## 2.4. DEFINIÇÕES SOBRE SISTEMAS DE SEGURANÇA (SIS)

A norma ANSI/ISA TR-84.01 exige que a indústria determine um Nível de Integridade Desejado (SIL – *Safety Integrity Level*) para todas as aplicações de Sistemas de Instrumentados de Segurança (SIS – *Safety Instrumented Systems*). A determinação do SIL é uma decisão que passa pela análise de risco do processo, (PHA – *Process Harzard Analysis*), e inclui a avaliação do equilíbrio entre a probabilidade do evento, sua severidade e tolerância ao mesmo. Os métodos utilizados para a avaliação do SIL de uma malha controle, são:

- Lista de verificação (Checklist);

- E se (What if);

- E se / lista de verificação (What if/checklist);

- FMEA (análise do modo de falha e seus efeitos) (failure mode and effects analysis);

- FTA análise da árvore de falhas (fault tree analysis);

- HAZAN Analise de riscos (Hazard Analysis);

- HAZOP estudo de riscos e operacionalidade (hazard and operability study);

- FTA HAZOP.

Nos EUA, a OSHA (Occupational Safety and Heath Organization) e a EPA (Environment Program Agency), através de seus programas PSM (Process Safety Management) e RPM (Risc Manegement Program) exigem que se faça uma análise de risco do processo, e a utilize como base para tomar medidas para a proteção dos trabalhadores, da comunidade e do meio ambiente. Um programa adequado deve incorporar a assim chamada "Boa prática de Engenharia", que significa na prática seguir as normas e padrões emitidos por organizações tais como: ASME, API, ANSI, NFPA, ASTM, etc.

Em fevereiro de 1996, a ISA editou o Standard ISA TR-84.01 "Aplicação de Sistemas de Segurança Instrumentados nas Indústrias de Processo". Em início de 1997, esta norma foi elevada à categoria de ANSI, ou seja, passou a ser de aplicação legalmente obrigatória. Obedecer esta norma, nos EUA não é uma opção, já que a não obediência pode resultar em ação civil e criminal, tanto contra as empresas como contra os indivíduos envolvidos (GRUHN; CHEDDIE, 2006).

Tanto a norma ANSI/ISA TR-84.01 como a IEC 61508 exigem que se defina um Nível de Integridade Desejado (SIL) para cada Sistema de Intertravamento de Segurança.

O SIL (Nível de Integridade de Segurança) é uma classificação de risco determinada a partir da probabilidade de falha sob a demanda. É muito importante levar em conta o impacto da confiabilidade e o modo de falha dos instrumentos de campo no SIL, o que frequentemente era esquecido quando se via um SIS apenas como o equipamento eletrônico contido no gabinete do sistema de *shutdown*. É

possível correlacionar um SIL às exigências de seus respectivos SIS. A IEC 61508 reconhece 4 níveis de SIL, enquanto a TR-84.01 de 1996 só reconhece os níveis de 1 a 3 (FINKEL *et al.*, 2006).

#### 2.4.1. Falhas

Se analisado com atenção a ISA TR-84.01, as falhas podem ser caracterizadas das seguintes formas:

- Falhas aleatórias: uma falha espontânea de componente (hardware).

As falhas aleatórias podem ser permanentes (existem até serem eliminadas) ou intermitentes (ocorrem em determinadas circunstancias e desaparecem em seguida).

- Falhas sistemáticas: uma falha escondida dentro do projeto ou montagem (hardware ou tipicamente software) ou falhas devido a erros (incluindo-se enganos e omissões) nas atividades de ciclo de atividades de segurança que fazem o SIS falhar em determinadas circunstâncias, sob determinadas combinações de entradas ou sob uma determinada condição ambiental.

- Falha em modo comum: o resultado de um defeito em modo comum.

- Defeito em modo comum: uma única causa que pode causar falhas em vários elementos do sistema. A única causa pode ser interna ou externa ao sistema.

As falhas detectáveis são aquelas que o próprio SIS consegue observar sua ocorrência, sinalizando tal fato e permitindo que se executem as devidas ações corretivas. Falhas não detectáveis são aquelas não percebidas pelos mecanismos de detecção e que permanecem residentes no SIS.

Outra classificação das falhas, que ocorrem em SIS, dada por Globe e Cheddie (2005), relaciona-se aos efeitos que tais falhas possam acarretar. Se as consequências forem inseguras, a falha é dita como sendo insegura. Por outro lado,

se as consequências não provocarem situações inseguras, a falha é classificada como sendo segura.

Um sistema implementado através de uma arquitetura tolerante a falhas, normalmente supõe a existência de módulos de controle e intertravamento redundantes. A ocorrência de uma falha do tipo inseguro e não detectável em um dos módulos da arquitetura permanece no sistema sem, no entanto, causar situações inseguras, pelo menos em um primeiro momento. Por outro lado, podem ocorrer falhas compensatórias em outros módulos, ou seja, falhas que afetem o funcionamento dos demais módulos do sistema da mesma forma que a falha insegura do primeiro módulo.

Desta forma, o dispositivo comparador da saída de cada módulo irá ser induzido a produzir saídas incorretas, gerando condições inseguras para o SIS. Se este não dispuser de módulos redundantes, a falha inicialmente descrita, por si só, já será capaz de produzir estados inseguros no SIS.

No entanto, há uma consideração que ameniza o impacto das falhas não detectáveis e inseguras no sistema. Os circuitos integrados com alta escala de integração possuem altas taxas de falhas, quando comparados com componentes convencionais e mesmo circuitos integrados com pequena e média escala de integração. No entanto, apenas uma pequena parcela dessa taxa de falhas refere-se a situações que irão provocar estados inseguros no sistema. Isto ocorre porque a maioria das falhas acaba por desabilitar completamente o funcionamento de um circuito integrado, e apenas uma parcela mínima dessas falhas irá, de fato, estabelecer condições inseguras no SIS.

A N-2595 define as falhas da seguinte forma (PETROBRAS, 2002):

- Fail Safe (Falha Segura): resultado de uma falha em um componente ou sistema, cujo estado final deve ser mais seguro ou menos perigoso.

- Falha: n\u00e3o cumprimento do servi\u00f3o esperado de um dispositivo.

- Falha Espúria: falha cujo resultado implica ação de pelo menos um atuador, sem que tenha ocorrido realmente um evento iniciador que o demandasse.

- Falha na Demanda: falha que se caracteriza pela não ação ou ação incorreta de pelo menos um atuador, quando da ocorrência de um evento iniciador que demande essa ação.

Falha Oculta: falha cuja ocorrência só é percebida quando a ação de uma malha de segurança é solicitada, seja por demanda ou teste.

## 2.4.2. Análise Quantitativa e Qualitativa

Há duas formas principais para se efetuar uma Análise de Segurança, que são a análise do tipo qualitativo e a análise do tipo quantitativo. Antes que se possam obter valores numéricos, através de uma análise quantitativa, é indispensável à realização de uma análise qualitativa eficiente, sem a preocupação de se atribuir valores às ocorrências. Uma análise quantitativa não deve desviar o foco dos problemas existentes, tais como falhas de projeto. Uma das principais utilidades deste tipo de análise é se fazer uma comparação entre sistemas com funções similares.

A Análise Qualitativa procura identificar mecanismos que programem os requisitos especificados, de forma que se mantenha o nível de segurança de um Sistema Crítico durante sua operação (SEAMAN, 1999).

De acordo com Gruhn (2006) atualmente tem sido dada à preferência para a técnica HAZOP (*Hazard Operability*), sem dúvida a melhor para identificar riscos, porém demorada, cansativa e exige um grande volume de recursos. Se o processo que estiver sendo analisado for bem conhecido, talvez seja melhor usar a técnica de "listas de verificações" (*check list*). Se, por outro lado o processo envolver uma grande quantidade de equipamento mecânico interdependente pode ser melhor usar a técnica da Análise de Modos de Falhas e seus Efeitos (FMEA). Existe ainda a técnica que é preconizada pela API (*American Petroleo Institute*) chamada "Avaliação de Função de Segurança" (SAFE – *Safety Function Evaluation*), na qual se preenche um mapa Safe. É uma técnica semelhante à FMEA, já que aqui também se usa o modo de falha de cada equipamento.

A Análise de Risco deve também especificar a taxa aceitável de falha segura. A taxa de falha segura é normalmente chamada de "trip" falso, parada inconveniente ou taxa de "trips" espúreos. A taxa de falha segura ou espúrea é incluída na análise do sistema de segurança de um sistema, já que a partida e a parada de um processo são ocasiões com alta probabilidade de ocorrência de um evento perigoso.

É por isso que, em muitos casos, a diminuição de paradas espúreas aumenta a segurança do processo. A taxa aceitável de falha segura é comumente expressa como o tempo médio para uma falha segura ou espúrea (MTTF<sub>sp</sub>). As falhas seguras são também muito indesejáveis por reduzirem a produção, causar refugos e outros problemas que variam em função de cada processo considerado (FINKEL *et al.*, 2006).

## 2.4.3. Probabilidade de Falha sobre Demanda (PFD)

Se o risco inerente ao processo for considerável aceitável, não existe necessidade de reduzi-lo, mas se ele for considerado maior do que aceitável é preciso reduzi-lo. Uma primeira atitude é procurar alterar o processo, ou seu controle, se isso não resolver, deve-se usar dispositivos de segurança autônomos, como válvula de alívio de pressão, discos de rupturas e etc.

Se tudo isso não resolver, então deve-se projetar o SIS para reduzir o risco a um nível aceitável. Este estudo de risco e redução do fator de risco (RRF – *Risk Reduction Factor*) antecede à especificação do SIS e deve ser feito para cada função de segurança (SIF - *Safety Instrumented Function*) (GRUHN;CHEDDIE, 2006).

PFD é a probabilidade de uma malha de segurança falhar em resposta a uma demanda (N-2595, PETROBRAS, 2002).

Segundo Finkel *et al.* (2006, p. 579), "O conceito de disponibilidade é bastante difundido. Assim, se um equipamento tem uma disponibilidade de 99%, significa que ele pode operar durante 99% do tempo disponível durante sua vida útil, e estará inoperante durante o 1% restante".

Partindo da idéia de que poderá ocorrer um acidente quando houver uma demanda do SIS e ele estiver indisponível. Então, o risco de ocorrer um acidente fica dependendo da PFD e da frequência da demanda.

Então, pode-se dizer que:

$$PFD = 1 - D, (1)$$

onde D é a disponibilidade.

$$RRF = \frac{1}{PFD},\tag{2}$$

onde RRF é o fator de redução de risco.

De acordo com Gruhn e Cheddie (2006) SISs devem ser projetados para falhar em uma direção segura em caso de falha de um componente individual, perda de sinal, e perda da alimentação de energia (elétrica ou ar de instrumentação). Exceto para aquelas poucas aplicações necessitando de uma configuração de energizado para parar, exemplo: válvula de controle ar para fechar. SISs devem ser projetados para paralisar o processo em caso de falta de energia. Se a aplicação demanda circuitos que são energizados para parar, é necessário um diagnóstico especial e um sistema de suprimento de energia *back-up*.

A Tabela 2 mostra como são distribuídos os níveis do SIL.

TABELA 2 - SIL EM FUNÇÃO DE DISPONIBILIDADE E PROBABILIDADE DE FALHA SOB DEMANDA

| DEIVIANDA         |                   |              |                |

|-------------------|-------------------|--------------|----------------|

| Nível de          | Disponibilidade   | PFD          | RRF            |

| integridade (SIL) | (segura) desejada |              |                |

| 4                 | 99,99 %           | 0,01%        | >10.000        |

| 3                 | 99,90 a 99,99 %   | 0,01 a 0,1 % | 1.000 a 10.000 |

| 2                 | 99,00 a 99,90 %   | 0,1 a 1 %    | 100 a 1.000    |

| 1                 | 90,00 a 99,00 %   | 1 a 10 %     | 10 a 100       |

|                   |                   |              |                |

FONTE: FINKEL et al. (2006) - IEC 61508.

A taxa de falha é normalmente representada pela letra grega minúscula lambda (λ). É comum a utilização de unidades de "falhas por milhão de horas" ou "falhas por ano" (GLOBE;CHEDDIE, 2005).

Segundo Piazza (2000) a taxa de falhas é a frequência com que as falhas ocorrem num certo intervalo de tempo. É medida pelo número de falhas para cada hora de operação ou número de operações do sistema.

$$\lambda = \frac{N\acute{u}mero de falhas por ano}{horas por ano}.$$

(3)

Goble (1998) demostra que uma taxa constante de falha está relacionada com MTTF (tempo médio de falha) de acordo com a equação abaixo.

$$\lambda = \frac{1}{MTTF}. (4)$$

Mean Time to Repare (MTTR) é um termo criado para incluir claramente tanto tempo de detecção de diagnóstico e tempo real de reparo. Na verdade MTTR é uma estimativa de tempo para, reconhecer e identificar a falha; tempo para obter peças sobressalentes; tempo para adquirir pessoas para a equipe; tempo real para fazer o reparo; tempo para documentar todas as atividades, e tempo para obter os equipamentos em funcionamento.

O tempo médio entre falhas (*MTBF*) é definido como a média de tempo de uma falha mais o tempo médio de reparação. Inclui o tempo de falha, o tempo necessário para detectar a falha, e tempo real de reparação.

$$MTBF = MTTF + MTTR. (5)$$

$$Disponibilidade = \frac{Tempo \quad Disponível}{Tempo \quad Total}.$$

(6)

$$Disponibilidade = \frac{Tempo \quad Disponivel}{\left(Tempo \quad Disponivel + Indisponivel\right)}. \tag{7}$$

$$D = \frac{MTBF}{(MTBF + MDT)},\tag{8}$$

onde MDT é o tempo médio indisponível.

$$\lambda_{S} = \frac{MTTF}{(MTBF + MTTR)},\tag{9}$$

onde  $\lambda_s$  é a taxa de falha segura.

Para falhas perigosas, o tempo indisponível deve englobar não apenas o tempo para reparo, mas também o tempo de "descoberta", ou seja, o tempo decorrido antes que se torne conhecimento da existência do problema.

$$\lambda_d = \frac{MTBF}{\left(MTBF + \left(\frac{TI}{2}\right) + MTTR\right)},\tag{10}$$

onde TI é o intervalo de testes e  $\lambda_d$  é igual a falha perigosa.

Estas fórmulas somente são validas para sistemas simples, não redundantes (Finkel *et al.*, 2006).

Para sistemas redundantes pode-se seguir a Tabela 3.

TABELA 3 – CÁLCULO DE PFD E MTTF<sub>SD</sub> PARA SISTEMAS REDUNDANTES

| Configuração | MTTF <sub>sp</sub>       | PFD                            |

|--------------|--------------------------|--------------------------------|

| 1 de 1       | $1/\lambda_{\rm s}$      | $\lambda_d^*$ (TI/2)           |

| 1 de 2       | $1/(2^*\lambda_s)$       | $((\lambda_d)^2 * (TI)^2) / 3$ |

| 2 de 2       | $1/(2*\lambda_s^2*MTTR)$ | λ <sub>d</sub> * TI            |

| 2 de 3       | $1/(6*\lambda_s^2*MTTR)$ | $(\lambda_d)^2 * (TI)^2$       |

FONTE: FINKEL et al. (2006) - IEC 61508.

## 2.4.4. Análise de Sistemas

## 2.4.4.1. Análise de um Sistema a Rele

Assumindo que um rele industrial tenha um *MTBF* de 100 anos. Assumir-se-á que se tenha um rele para cada entrada e saída no sistema. Irá se trabalhar com 8

entradas e 2 saídas, logo, irá se adicionar a taxa de falha segura de 10 reles. Assumindo um rele com 98% de taxa de falha segura.

$$MTTF_{sp} = \frac{1}{\lambda_s} = \frac{1}{\left(\frac{1}{100}\right) * 0.98 * 10} = 10.2$$

anos (10 anos).

Quando há uma demanda de desligamento do sistema, ela vem em uma entrada apenas, as oito entradas não são acionadas ao mesmo tempo. Logo, deverse-á incluir apenas uma entrada e as duas saídas no modelo específico. Isso equivale a apenas três reles. Como os reles não têm diagnósticos, todas as falhas inseguras são inseguras e não detectáveis (GRUHN;CHEDDIE, 2006). A probabilidade de falha sobre demanda, o fator de redução de risco e a disponibilidade são calculados como mostrado abaixo:

$$PFD = \lambda_d * \left(\frac{TI}{2}\right)$$

$$PFD = \left(\frac{1}{100}\right) * 0.02 * 3 * \left(\frac{1 \text{ ano}}{2}\right)$$

$$PFD = 3e^{-4}$$

$$RRF = \frac{1}{PFD} = 3300$$

$$D = 1 - PFD$$

$$D = \left(1 - 3e^{-4}\right)$$

$$D = 0.9997 = 99.97\%.$$

2.4.4.2. Análise de um Sistema com Controlador Lógico Programável não redundante

Substituindo o sistema à rele por outro que utiliza um CLP de propósito geral, considerando:

MTBF da CPU = 10 anos.

MTBF do módulo de I/O = 50 anos.

Taxa de falha segura da CPU = 60%.

Taxa de falha segura do módulo de I/O = 75%.

$$MTTF_{sp} = \frac{1}{\lambda_s} = \frac{1}{\left(\left(\frac{1}{10}\right) * 0.6\right) + \left(\left(\frac{1}{50}\right) * 0.75 * 2\right)} = 11$$

anos,

2: representa 2 módulos de I/O.

Assumindo um diagnóstico de cobertura de 90% da CPU e 50% para o módulo de I/O. Assumindo-se que o PLC é realmente testado manualmente anualmente.

$$PFD = \lambda_d * \left(\frac{TI}{2}\right)$$

$$PFD = \left[\left(\left(\frac{1}{10}\right) * 0,4 * 0,1\right) + \left(\left(\frac{1}{50}\right) * 2 * 0,25 * 0,5\right)\right] * \left(\frac{1 \text{ ano}}{2}\right)$$

$$PFD = 4,5e^{-3}$$

$$RRF = \frac{1}{PFD} = 220$$

$$D = 1 - PFD$$

$$D = \left(1 - 4,5e^{-3}\right)$$

$$D = 0.9955 = 99,55\%.$$

Neste caso, verifica-se um desempenho de um sistema com CLP mais baixo do que um a rele. Assumindo que o CLP é realmente testado uma vez por ano (o que é um pressuposto excessivamente otimista para muitos sistemas). Um módulo de I/O com cobertura de diagnóstico de 50%, o que também é um pressuposto otimista para muitos sistemas de propósito geral. Mas, se percebe que CLPs de utilização geral são bons para intertravamento e ainda controle (GRUHN;CHEDDIE, 2006).

## 2.4.4.3. Análise de um Sistema de Redundância Tripla (TMR)

Assumindo os mesmos *MTBFs* de um CLP sem redundância e as mesmas taxas de falhas, pois o *hardware* é essencialmente o mesmo, só que no CLP redundante existe mais CPU e mais canais de comunicação. A configuração deste TMR é 2003.

$$MTTF_{sp} = \frac{1}{(6*(\lambda_s)^2 * MTTR)}$$

$$MTTF_{sp} = \frac{1}{6*\left[\left(\frac{1}{10}\right)*0,6\right) + \left(\left(\frac{1}{50}\right)*0,75*2\right)\right]^2 * \left(\frac{4 \text{ horas}}{8760 \text{ horas/ano}}\right)}$$

$$MTTF_{sp} = 45.000 \text{ anos.}$$

Adotando um diagnóstico de cobertura de 99% para a CPU e para o módulo de I/O, algo que poderá não acontecer em alguns sistemas. Assumindo que o CLP é realmente testado manualmente anualmente.

$$PFD = (\lambda_d)^2 * (TI)^2$$

$$PFD = \left[ \left( \left( \frac{1}{10} \right) * 0.4 * 0.01 \right) + \left( \left( \frac{1}{50} \right) * 2 * 0.25 * 0.01 \right) \right]^2 * \left( \frac{1 \text{ ano}}{2} \right)^2$$

$$PFD = 6.25e^{-8}$$

$$RRF = \frac{1}{6.25e^{-8}} = 16.000.000$$

$$D = 1 - (6.25e^{-8}) = 0.9999999375 = 99.9999375\%.$$

Os cálculos indicam que o sistema TMR tem um tempo médio entre "trips" de 45.000 anos, e um fator de redução de risco superior a dez milhões, isto daria mais do que SIL 4. É importante advertir que estes não são certificados para uso em SIL 4. A norma IEC 61508 é cautelosa para nível de integridade maior que SIL 4 (GRUHN;CHEDDIE, 2006).

#### 2.4.5. Causa Comum

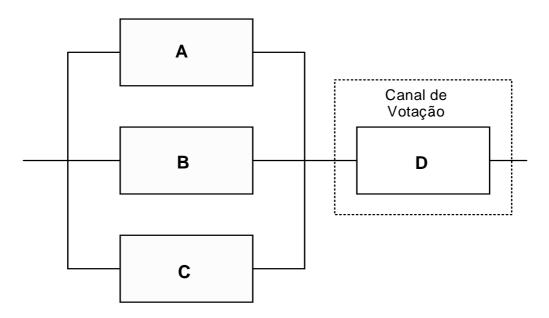

Uma falha pode acarretar uma falha geral do sistema redundante. Exemplos ambientais típicos são calor, vibração, excesso de tensão, etc. Um método de quantificar causa comum é referido como o fator  $\beta$ . Este fator representa a percentagem de falhas identificadas em uma parte do sistema que pode impactar em canais múltiplos, e o sistema poderá falhar de uma só vez. Por exemplo, se um sistema redundante tem um fator  $\beta$  = 1%, isso significa que, todas as falhas identificadas, das quais 1% poderia ocorrer em vários canais ao mesmo tempo e fazer todo o sistema falhar. 1% é suficiente para preocupar-se? E cerca de 10%? (FINKEL *et al.*, 2006).

Causa comum pode ser definida como um único problema que afeta múltiplos componentes. Como mostrado na Figura 3 (A, B e C), representam um sistema triplo. No entanto, se o item D falhar, todo o sistema falha. Este fator representa o percentual de falhas identificadas em uma fatia do sistema que irá afetar todo o sistema. O fator  $\beta$  foi derivado a partir de estudos empíricos. Smith (1997) sugere um intervalo típico para  $\beta$  = 20% quando se utiliza componentes idênticos redundantes (como é feito com a maioria dos sistemas).

FIGURA 3 – CAUSA COMUM. FONTE: GRUHN e CHEDDIE (2006). Segundo Zio (2007), a confiabilidade de um sistema em paralelo é a probabilidade de um ou mais caminhos serem operacionais. Um sistema paralelo é um sistema em que não se considera haver falhas, a menos que todos os componentes tenham falhado. Como se observa na Figura 3, as falhas em um componente não influenciam na confiabilidade dos sistemas sobreviventes.

Uma configuração k-saída-de-n exige que pelo menos k módulos de um total de n devem estar operacionais para que o sistema esteja em funcionamento. Normalmente, um eleitor (votador) é necessário, se o eleitor é perfeito e todos os módulos possuem confiabilidade *R*, a equação para avaliar a confiabilidade desses blocos é (XIE; DAI; POH, 2004):

$$R = \sum_{i=k}^{n} \frac{n!}{i!(n-i)!} p^{i} (1-p)^{n-i},$$

(11)

onde R é a confiabilidade do sistema, n é o número de unidades e p é a confiabilidade de cada unidade.

## 2.5. TIPOS DE REDUNDÂNCIA

Um componente é sujeito à falha em qualquer modo, aberto ou fechado. A redundância pode ser utilizada para aumentar a confiabilidade de um sistema sem qualquer alteração na confiabilidade dos componentes individuais que formam o sistema (PHAM, 2003).

Segundo Piazza (2000), a confiabilidade de um sistema é a probabilidade de que, quando em operação sob condições ambientais estabelecidas, o sistema apresentará uma performance desejada (sem falhas) para um intervalo de tempo especificado e a redundância é a existência de mais de um meio para se atingir um objetivo determinado.

Finkel *et al.* (2006) comenta que a redundância deve ser utilizada para fornecer um sistema em operação constante, embora um ou mais instrumentos possam falhar.

A N-2595 sugere que técnicas de utilização de diferentes tecnologias, projetos, fabricação, *software*, *firmware*, etc., podem ser usados para se reduzir à

influência das falhas de causa comum. Exemplos de métodos que podem ser utilizados para se obter a redundância diversa (PETROBRAS, 2002):

- medição de diferentes variáveis de processo, tais como pressão e temperatura, nos casos onde o relacionamento entre as variáveis é bem determinado e conhecido;

- uso de diferentes tecnologias de medição sobre a mesma variável de processo, tais como medição de vazão por vortex e coriolis;

- uso de diversidade geográfica, isto é, rotas alternativas para meios de comunicação redundantes.

Para Storey (1996), a forma mais utilizada para a prevenção dos efeitos de falhas é a utilização de módulos redundantes. A redundância de *hardware* implica inclusão de circuitos de *hardware* adicionais ao mínimo necessário para o funcionamento do sistema e a redundância de *software* implica geração de versões distintas do *software* do sistema ou de partes desse *software*, sempre se baseando em uma especificação comum.

#### 2.5.1. Redundância de Hardware

O emprego de redundância em um Sistema Instrumentado de Segurança consiste na utilização de componentes auxiliares com a finalidade de realizar as mesmas funções desempenhadas por outros elementos presentes no sistema. A finalidade principal da utilização de redundância nesses sistemas é a prevenção de condições ou estados inseguros.

Embora a redundância sempre implique na adição de novos componentes, deve-se fazer o possível para não aumentar a complexidade do sistema, de forma a não se ter efeito contrário, ou seja, diminuição da confiabilidade e da segurança do sistema. Conforme colocado em Johnson (1989), a redundância de *hardware* pode ser implementada através de três formas básicas:

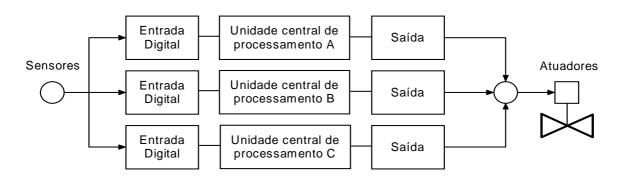

Redundância estática: utiliza o mascaramento de falhas como principal técnica. O projeto é feito de forma a não requerer ações específicas do sistema ou de sua operação em caso da ocorrência de falhas. Todos os elementos executam a mesma tarefa e o resultado é determinado por votação. Exemplos são TMR (*Triple Modular Redundancy*) e NMR (*N Modular Redundancy*);

FIGURA 4 – SISTEMA DE REDUNDÂNCIA MODULAR TRIPLA.

Um sistema paralelo sério consiste de *m* caminhos paralelos e cada caminho possui *n* unidades conectadas em séries. Para calcular a confiabilidade utiliza-se a equação12 (ZIO, 2007).

$$R = 1 - (1 - p^n)^m, (12)$$

onde R é a confiabilidade e p é a confiabilidade de cada unidade.

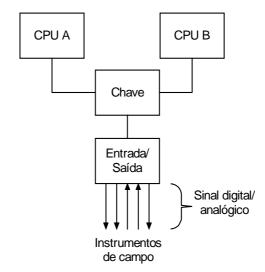

Redundância dinâmica: implica na detecção de falhas, caso em que o sistema deve tomar alguma ação para anular seus efeitos, o que normalmente envolve uma reconfiguração do sistema. Costuma ser usada em aplicações que suportam permanecer em um estado errôneo durante um curto período de tempo, tempo esse necessário para a detecção do erro e recuperação para um estado livre de falhas. Um exemplo de implementação de redundância dinâmica é através de módulos estepes (hot standby).

FIGURA 5 - SISTEMA HOT STANDBY.

Redundância híbrida: consiste na combinação de técnicas estáticas com técnicas dinâmicas. Utiliza mascaramento de falhas para prevenir que erros se propaguem, detecção de falhas e reconfiguração para remover, do sistema, unidades com falha.

#### 2.5.2. Redundância de Software

Simplesmente replicar *softwares* idênticos pode não ser uma estratégia muito eficaz. Rotinas idênticas de *software* vão apresentar erros idênticos. Logo, não basta copiar um programa e executá-lo em paralelo ou executar o mesmo programa duas vezes.

Um problema que surge é a falta de uma metodologia de eficiência reconhecida para a avaliação da segurança do *software* para os sistemas que precisam de segurança e que tem o *software* como componente crítico.

Pode-se dizer que a falta de experiência em especificações de software e das especificações em relação ao ambiente de aplicação representa um grave problema, fazendo com que o sistema atinja situações imprevistas, como consequência de procedimentos operacionais incorretos, de mudanças não esperadas no ambiente operacional, ou ainda de modos de falhas não previstas do sistema (JAFFE *et al.*, 1991).

Um caminho para se definir e avaliar melhor o conceito de segurança do software é através da definição de um conjunto de fatores que consigam representar adequadamente o conceito de segurança (KITCHENHAM; PELEEGER, 1996).

Em função da dificuldade da comprovação da não existência de falhas na implementação de um *software*, em relação à sua especificação, são utilizadas técnicas de redundância de *software*, cujo objetivo é tornar o *software* mais robusto em relação à segurança, ou seja, tolerante a falhas porventura ainda existentes (JOHNSON, 1989).

Segundo Burns e Wellings (1997) surge outras formas de redundância em software:

- Diversidade: também chamada programação diversitária, é uma técnica de redundância usada para obter tolerância à falhas em software. A partir de um problema a ser solucionado são implementadas diversas soluções alternativas, sendo a resposta do sistema determinada por votação (CHEN; AVIZIENIS, 1978).

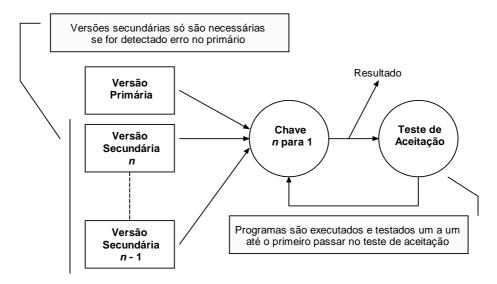

- Blocos de recuperação: nessa técnica programas secundários só serão necessários na detecção de um erro no programa primário. Essa estratégia envolve um teste de aceitação. Programas são executados e testados um a um até que o primeiro passe no teste de aceitação. A estratégia de blocos de recuperação tolera n-1 falhas, no caso de falhas independentes nas "n" versões. Como mostrado na Figura 6:

FIGURA 6 – BLOCOS DE RECUPERAÇÃO.

## 2.5.3. O Impacto da Redundância

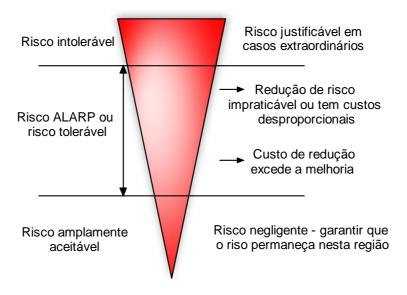

De acordo com Gruhn e Cheddie (2006, p. 139), "Duplo nem sempre é melhor do que simples, e triplo nem sempre é melhor do que duplo." Conforme mostrado na Figura 7,

|      |            | Probabilidades       |                        |

|------|------------|----------------------|------------------------|

|      | <b>—</b> © | Falha Segura         | Falha Perigosa         |

| 1001 | A          | 0.04<br>(25 anos)    | 0.02<br>(50 anos)      |

| 1002 | A B        | 0.08<br>(12.5 anos)  | 0.0004<br>(2,500 anos) |

| 2002 | A B        | 0.0016<br>(625 anos) | 0.04<br>(25 anos)      |

| 2003 | A B C      | 0,0048<br>(208 anos) | 0.0012<br>(833 anos)   |

FIGURA 7 – O IMPACTO DA REDUNDÂNCIA. FONTE: GRHUN e CHEDDIE (2006).

Analisando um sistema sem redundância, 1oo1, conforme indicado na Figura 7, um exemplo de falha segura é quando o rele de contato abre e desenergiza o sistema causando um "trip". Assumindo uma probabilidade de falha segura de 4% pelo período de um ano, significa que o sistema tem um *MTTF* (seguro) de 25 anos. Um exemplo de falha perigosa é quando o rele de contato não abre quando necessário não desenergizando o sistema. Assumindo uma probabilidade de falha perigosa de 2% pelo período de um ano, significa que o sistema tem um *MTTF* (perigoso) de 50 anos.

Um sistema 1002 tem suas saídas em série, isto quer dizer que o sistema precisa que pelo menos uma saída atue para que o sistema faça o *shutdown*, desta forma, a probabilidade de falha segura dobra para 8%, diminuindo o *MTTF* (seguro) para 12,5 anos. Mas, para ocorrer uma falha perigosa, ele precisa que 2 eventos

ocorram simultaneamente, então, a probabilidade de ocorrer uma falha perigosa é (0.02 \* 0.02) = 0.0004 o que faz com que o *MTTF* (perigoso) fique igual a 2.500 anos. Em outras palavras, um sistema 1002 é realmente muito seguro, mas aumenta a probabilidade de "trip" do processo.

Em sistemas 2002, os canais são ligados em paralelo, quando precisa-se desenergizar o sistema e um contato estiver colado, não irá ocorrer o *shutdown* caracterizando uma falha perigosa, como este sistema tem duas vezes mais hardware que um sistema simples, ele tem o dobro de probabilidade de ocorrer uma falha perigosa 4% que resulta em um *MTTF* (perigoso) de 25 anos. Para este sistema sofrer um "trip" é necessário que ocorra uma falha segura nos dois canais. A probabilidade de ocorrer dois eventos ao mesmo tempo é calculada pela probabilidade de um único evento ao quadrado, logo, (0,04\*0,04) = 0,0016 que corresponde a um *MTTF* (seguro) de 625 anos. Esta configuração reduz as paradas desnecessárias, mas aumenta o risco das falhas perigosas.

O Sistema 2003 é um sistema de votação por maioria, o que dois ou mais canais decidir é o irá acontecer com o sistema. Um sistema 1002 precisa ter duas falhas simultâneas para ocorrer uma falha perigosa, o 2003 também, como este sistema é triplo então ele tem três vezes mais dupla combinações de falha (A + B, A + C, C + B), logo, a probabilidade de falha perigosa dele é de 3 \* 0,0004 = 0,0012 fornecendo um *MTTF* (perigoso) de 833 anos. Agora, em sistema 2002 para acontecer um "trip" ele necessita que aconteçam falhas seguras nos dois canais, novamente o sistema 2003 triplicou a dupla falha segura do sistema 2002 gerando uma probabilidade de 3 \* 0,0016 = 0,0048 apresentando um *MTTF* (seguro) de 208 anos (GRUHN; CHEDDIE, 2006).

#### 2.6. SISTEMAS EMBARCADOS

Sistemas embarcados são geralmente projetados para aplicações específicas, são o oposto dos sistemas construídos para aplicações genéricas. Os computadores pessoais são exemplos de sistemas de uso geral, projetados para atender várias aplicações distintas. São sistemas sujeitos a uma atualização contínua do *software* a ser executado, o que não ocorre nos sistemas embarcados,

uma vez programada uma aplicação específica, esta não sofrerá modificações ao longo da sua vida. Por exemplo, não se espera o melhoramento do *software* de um forno microondas após a sua venda. Contudo, com a evolução da complexidade dos sistemas embarcados, observa-se, cada vez mais, a necessidade de atualizações frequentes dos aplicativos a serem executados nos mesmos. Como o caso dos telefones celulares, que incorporam gradualmente diversas modificações no *software* executado.

A demanda por equipamentos inteligentes e soluções dedicadas, capazes de apresentar resultados eficientes para problemas, transforma a utilização de microprocessadores e sistemas embarcados em uma parcela importante do mercado de computação. Desta maneira, a demanda por sistemas operacionais embarcados que tenham a capacidade de comandar novos dispositivos e equipamentos é crescente e irreversível (ORTIZ, 2001).

Um sistema embarcado é uma junção do *hardware* e do *software* de um computador, projetados para executar uma tarefa específica (BARR, 1999).

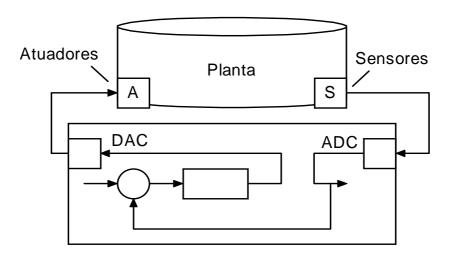

#### 2.6.1. Sistema de Tempo Real

É importante diferenciar Sistema de Tempo Real e Sistema Operacional de Tempo Real. Sistema de Tempo Real é um conjunto de todos os elementos especificados para essa finalidade, como *hardware*, sistema operacional e aplicativos. O Sistema Operacional de Tempo Real é um elemento do sistema completo de tempo real (OLIVEIRA, 2001).

Um sistema é classificado como de tempo real quando a execução de toda e qualquer tarefa devem se dar dentro de uma faixa de tempo estipulada *a priori*. Isto é importante para que o sistema possa realizar tarefas periódicas ou reagir a estímulos do meio sempre dentro de um tempo previsível. No caso da automação industrial esse tempo depende das constantes de tempo do processo a serem controladas (OLIVEIRA, 2001).

Aplicações com tempo real com restrições de tempo real são menos interessadas em uma distribuição uniforme dos recursos e mais interessadas em atender requisitos, tais como, períodos de ativação e *deadlines*. Essas aplicações

são usualmente organizadas na forma de várias *threads* ou tarefas concorrentes, logo um requisito básico para os sistemas operacionais de tempo real é oferecer suporte para tarefas e *threads* (OLIVEIRA, 2001).

As tarefas são abstrações que incluem: um espaço de endereçamento próprio (possivelmente compartilhado), um conjunto de arquivos abertos, um conjunto de direitos de acesso, um contexto de execução formado pelos registradores do processador.

As *Threads* são tarefas leves, únicos atributos são aqueles associados com o contexto de execução. Portanto, o chaveamento entre duas *threads* de uma mesma tarefa é muito mais rápido.

Uma aplicação tempo real é tipicamente um programa concorrente formado por tarefas e/ou *threads* que se comunicam e seguem um certo sincronismo. Existem duas grandes classes de soluções para programação concorrente: Troca de Mensagens e Variáveis Compartilhadas.

Os Sistemas de tempo real lidam com periféricos especiais, ou seja, diferentes tipos de sensores e atuadores, usados na automação industrial e controle de equipamentos em laboratório. O projetista da aplicação deve ser capaz de desenvolver os seus próprios *drivers* de dispositivos e incorporá-los ao sistema operacional (OLIVEIRA, 2001).

#### 2.6.2. Windows CE

Windows CE (*Compact Edition*) é uma versão da popular linha de sistemas operacionais da Windows para dispositivos portáteis. É suportado no Intel x86 e compatíveis como, MIPS, ARM, e processadores Super Hitachi.

Algumas características do Windows CE (MICROSOFT, 2009):

- Compacto;

- Alta velocidade em relação a outros Sistemas Operacionais;

- Interface gráfica;

- Baixo custo da licença;

- Ocupa pouco espaço de memória;

- Portável de forma a rodar em diversos processadores e tipos de hardware;

- Modular (permitir uma adaptação rápida e fácil a um sistema particular);

- Compatibilidade com a API Win32;

- Disponibiliza processamento em tempo real (crítico em determinados sistemas embarcados);

- Implementa uma política agressiva de gestão de energia.

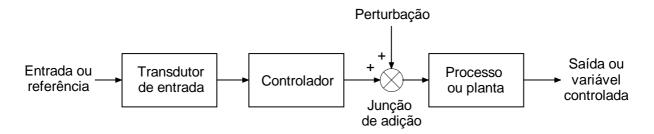

Oferece um controle industrial em tempo real com um trajeto de migração de custo flexível e baixo, controlando inclusive até o chão de fábrica.